нарушений будет констатироваться

наихудший случай. Следующим эта

пом работы над проектом будет уточ

нение места, где возникло наруше

ние правила проектирования. Для

этого следует запустить программу

анализа целостности сигналов, вы

брать упомянутую в отчёте цепь и

промоделировать распространение

сигналов в ней. В случае нарушения

допустимых значений импедансов

моделирование может не потре

боваться – достаточно будет изме

нить ширину проводников указан

ных цепей.

Кроме того, что в редакторе печат

ных плат проверка целостности сиг

налов является частью проверки DRC,

для верификации и отладки участков

платы, не удовлетворяющих правилам,

используется панель Signal Integrity,

как и в редакторе схем. Рассмотрим

ещё один пример, который идёт в

комплекте с программой и наглядно

демонстрирует особенности анализа

целостности на уровне платы.

Откроем проект Examples\Signal In

tegrity\SimpleFPGA\SimpleFPGA_SI_De

mo.PrjPCB и откроем плату этого про

екта. Внешний вид топологии, с из

лишними изгибами и удлинёнными

параллельными участками, уже на

водит на мысли о возможных пробле

мах. Для данного проекта были зада

ны правила проектирования (

De

sign

>

Rules

), и можно приступить к

анализу:

Tools

>

Signal Integrity

. Как и в

случае с предтопологическим анали

зом, игнорируем сообщение, что не

все компоненты содержат модели, и

получаем результат в виде панели Sig

nal Integrity. Здесь розовым показаны

цепи, для которых контролируемые

значения превышают заданные в пра

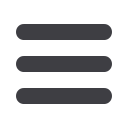

вилах нормы. Например, найдём цепь

D7 и, нажав на ней правой клавишей,

выберем команду

Cross Probe

>

To PCB

,

в результате чего проблемная цепь бу

дет показана на плате. Топология

этой цепи далека от идеала, и если,

например, оптимизировать эту цепь,

заменив меандр прямой дорожкой, то

будут получены следующие результа

ты для максимально допустимого

значения положительного выброса

на заднем фронте сигнала 299,7 мВ

(было 679,5 мВ). То есть теперь по это

му параметру топология удовлетво

ряет требованиям проекта, но топо

логию нужно далее редактировать,

чтобы привести в норму другие ха

рактеристики. Полные результаты

ПРОЕКТИРОВАНИЕ И МОДЕЛИРОВАНИЕ

64

WWW.SOEL.RUСОВРЕМЕННАЯ ЭЛЕКТРОНИКА

◆

№ 8 2010

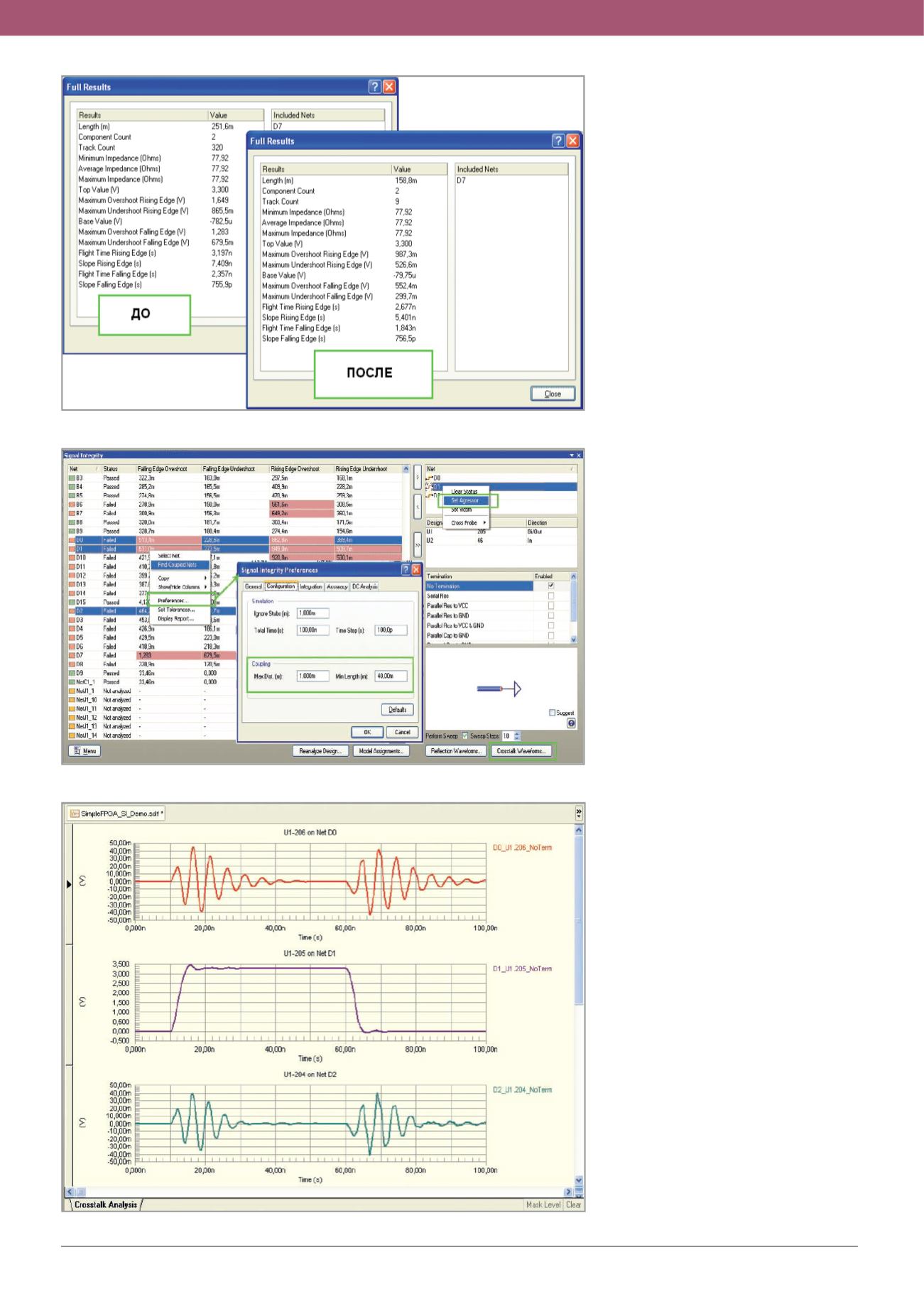

Рис. 7. Настройки для анализа перекрёстных помех

Рис. 8. Результат моделирования перекрёстных помех

Рис. 6. Результаты моделирования цепи D7 до и после редактирования

© СТА-ПРЕСС