можно выполнить на этапе схемы

(предтопологический анализ) и на

этапе платы (посттопологический).

Причём в первом случае программа

не учитывает расположение печат

ных проводников по слоям и ис

пользует усреднённое значение для

длины и волнового сопротивления

проводников. На схемном уровне

устранение проблем, связанных с

целостностью сигналов, происхо

дит путём согласования линий пере

дачи и входных/выходных сопро

тивлений микросхем. Рассмотрим по

отдельности оба представленных

выше подхода.

П

РЕДТОПОЛОГИЧЕСКИЙ АНАЛИЗ

Для знакомства с основными эта

пами проведения анализа целост

ности сигналов в Altium Designer

воспользуемся демонстрационным

проектом, который поставляется в

составе установочного диска и рас

положен в директории …Program

Files\Altium Designer Summer 09\Ex

amples\Signal Integrity\Spirit Level.

Откроем из этой директории файл

Signal Integrity.DsnWrk, который пред

ставляет собой группу из четырёх

проектов. Начнём с проекта SCH Is

sues.PrjPcb и откроем главную схему

проекта.

Анализ целостности начинается с

выполнения команды

Tools

>

Signal

Integrity

, при этом могут быть сооб

щения о том, что не все модели име

ются в наличии и что необходимо

задать усреднённую длину проводни

ков. Оба эти шага при появлении сле

дует пропустить (в первом случае

нажатием кнопки Continue, во вто

ром – Analyze Design), т.к. эту инфор

мацию можно задать через панель

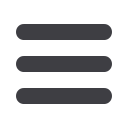

Signal Integrity (рис. 1), которая по

явится далее.

В левой части панели Signal In

tegrity показан список цепей, для ко

торых проводился анализ. Это те це

пи, которые объединяют компонен

ты с подключенными IBIS моделями

(о подключении моделей будет сказа

но отдельно в конце статьи). Если

найти в списке цепь с названием

DONE, то можно обнаружить, что для

неё рассчитанное значение Rising

Edge Overshoot (максимально допус

тимый положительный выброс на

переднем фронте сигнала) значи

тельно превышает аналогичные зна

чения для других цепей. Выбираем

левой клавишей цепь DONE и добав

ляем её в правый список, как показа

но на рисунке 1. После этого справа

под списком цепей (где сейчас ука

зана только одна цепь DONE) можно

увидеть все выводы, которые соеди

няет эта цепь. Убедившись, что в

списке Termination (согласованная

нагрузка) выбрана опция No Termi

nation, запускаем анализ кнопкой Re

flection Waveforms.

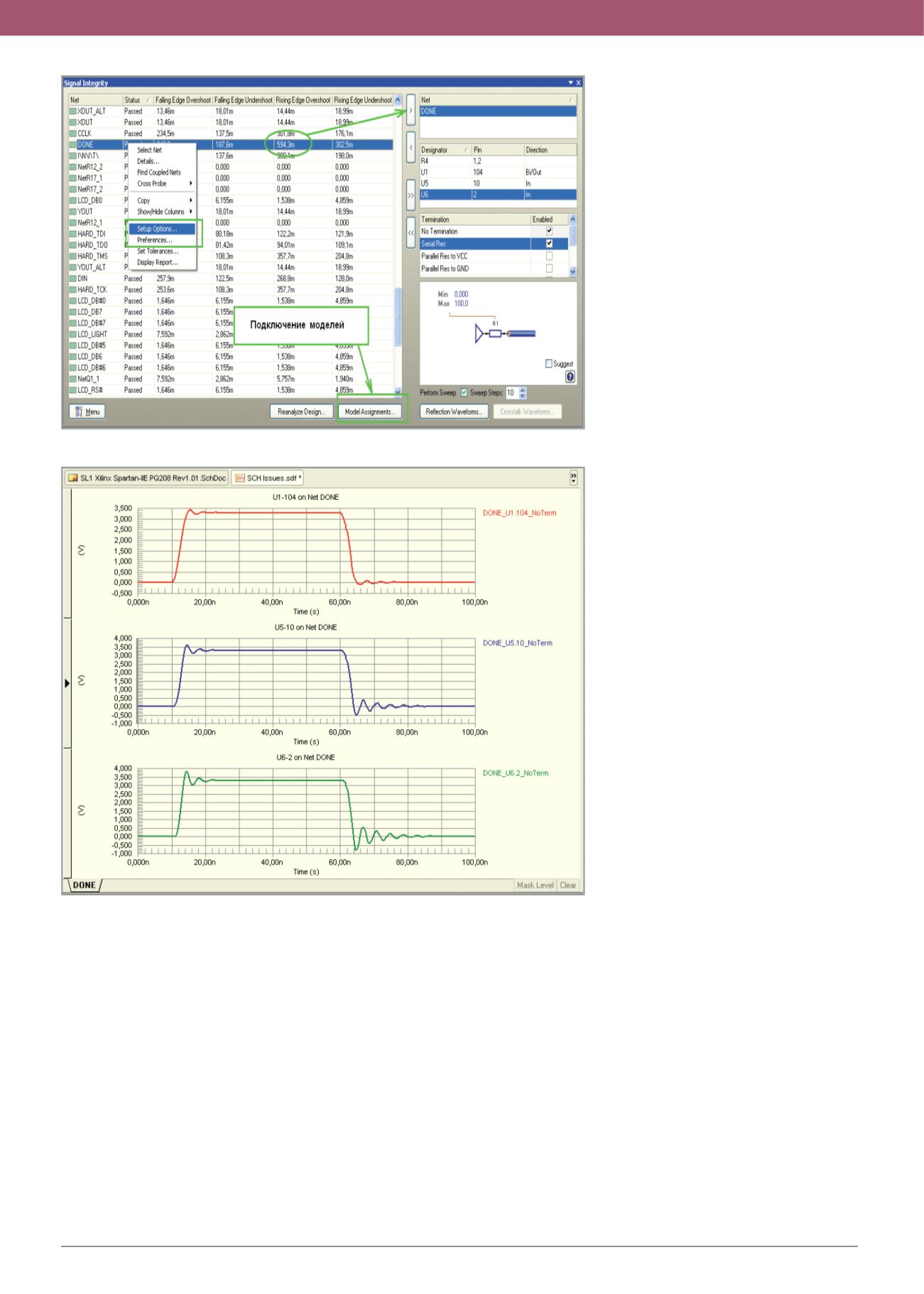

Результатом анализа будет отобра

жение трёх графиков, и чтобы их

проанализировать, можно временно

закрыть панель Signal Integrity. Гра

фики (рис. 2) показывают форму сиг

нала на источнике сигнала и двух

приёмниках, причём из графика вид

но, что на выводе микросхемы U6

имеются довольно большие выбросы,

которые могут повлиять на правиль

ность работы схемы. Под выбросами

понимаются минимальные и макси

мальные напряжения, имеющие мес

то после переключения сигнала меж

ду логическими уровнями. Такие выб

росы являются следствием отражения

сигнала из за неправильного согла

сования. Недостатком предтопологи

ческого анализа является отсутствие

возможности задать предельно допус

тимые значения для выбросов сигна

лов (это можно сделать лишь на уров

не платы).

ПРОЕКТИРОВАНИЕ И МОДЕЛИРОВАНИЕ

60

WWW.SOEL.RUСОВРЕМЕННАЯ ЭЛЕКТРОНИКА

◆

№ 8 2010

Рис. 2. Результат моделирования сигнала DONE с характерным «звоном» вследствие отражения

Рис. 1. Панель Signal Integrity используется для запуска моделированияе

© СТА-ПРЕСС