ПРОЕКТИРОВАНИЕ И МОДЕЛИРОВАНИЕ

63

WWW.SOEL.RUСОВРЕМЕННАЯ ЭЛЕКТРОНИКА

◆

№ 8 2010

●

Overshoot – Falling Edge – опреде

ляет максимально допустимый от

рицательный выброс (затухающие

колебания относительно низкого

значения напряжения) на заднем

фронте импульса сигнала;

●

Overshoot – Rising Edge – определяет

максимально допустимый положи

тельный выброс (затухающие коле

бания относительно высокого зна

чения напряжения) на переднем

фронте сигнала;

●

Signal Base Value – определяет

максимально допустимое значе

ние напряжения сигнала низкого

уровня;

●

Signal Flight Time Falling Edge – опре

деляет максимально допустимое

время задержки заднего фронта сиг

нала;

●

Signal Flight Time Rising Edge – опре

деляет максимально допустимое вре

мя задержки переднего фронта сиг

нала;

●

Signal Stimulus – определяет ха

рактеристики входных сигналов,

которые используются при анали

зе целостности сигналов. Это сиг

налы, которые подаются на каж

дый входной вывод тестируемой

цепи и формируются на выходных

выводах. Во время проверки пра

вил проектирования возвращает

ся наихудший возможный резуль

тат;

●

Signal Top Value – определяет ми

нимально допустимое значение

напряжения сигнала высокого

уровня;

●

Slope – Falling Edge – определяет мак

симально допустимое значение кру

тизны заднегофронта импульса. Под

этим значением здесь подразумева

ется время, затраченное на измене

ние уровня сигнала от порогового

напряжения (VT) до действительно

го значения напряжения низкого

уровня (VIL);

●

Slope – Rising Edge – определяет

максимально допустимое значе

ние крутизны переднего фронта

импульса. Под этим значением

здесь подразумевается время, за

траченное на изменение уровня

сигнала от порогового напряже

ния (VT) до действительного зна

чения напряжения высокого уров

ня (VIH);

●

Undershoot – Falling Edge – определя

ет максимально допустимое значе

ние положительного выброса (зату

хающие колебания относительно

низкого значения напряжения) на

заднем фронте сигнала;

●

Undershoot – Rising Edge – опреде

ляет максимально допустимое

значение отрицательного выбро

са (затухающие колебания относи

тельно высокого значения напря

жения) на переднем фронте сиг

нала;

Следует помнить, что данные пра

вила не контролируются при инте

рактивной трассировке, а использу

ются только при проверке DRC в па

кетном режиме. Для того чтобы

использовать эти правила, необходи

мо обязательно установить правила

Signal Stimulus Rule и Supply Nets rules

(о чём было сказано в предыдущем

разделе).

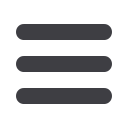

При запуске программы пакетной

проверки правил проектирования

DRC необходимо включить контроль

всех необходимых правил из числа

назначенных. Это производится в

окне Design Rule Check, где после на

жатия на кнопку Signal Integrity откро

ется специальное окно Design Rules с

активными опциями, соответствую

щими назначенным наборам правил

(рис. 5). После включения всех необ

ходимых опций следует запустить

процедуру проверки нажатием кноп

ки Run DRC.

В ходе проверки будет сформиро

ван отчёт, в котором в виде списка

Реклама

Телефон: +7 (495) 220-64-93, (981) 709-04-82, (960) 276 28 41

Факс: +7 (812) 333-27-55 (авт.)

•

info@spectr

pcb.ru•

www.spectr

pcb.ruРис. 5. Настройка проверки правил проектирования

© СТА-ПРЕСС