Программируемые логические ин

тегральные схемы, представленные

сегодня на рынке, отличаются друг

от друга по многим параметрам, на

пример, технологией производства,

объёмом встроенной памяти, наличи

ем аппаратных умножителей и т.п.

Характеристики конкретной ПЛИС

определяют подходы к решению той

или иной задачи, однако существуют

области специального применения

ПЛИС.

Р

ЕЖИМ

F

LASH

*F

REEZE

Программируемые логические ин

тегральные схемы корпорации Actel

семейств Igloo и ProASIC3L поддержи

вают режим низкого энергопотребле

ния Flash*Freeze. В этом режиме мик

росхемы потребляют чрезвычайно

низкую мощность, но не теряют дан

ные, сохранённые в регистрах и ОЗУ.

Микросхемы семейства Igloo nano по

ЭЛЕМЕНТЫ И КОМПОНЕНТЫ

30

WWW.SOEL.RUСОВРЕМЕННАЯ ЭЛЕКТРОНИКА

◆

№ 8 2010

Режим Flash*Freeze ПЛИС Actel

Евгений Котельников (Санкт Петербург)

Корпорация Actel поставляет ПЛИС, поддерживающие режим

микромощного потребления Flash*Freeze. Эта особенность, наряду

с мгновенным стартом микросхем, позволяет расширить область

применения ПЛИС Actel. В статье обсуждаются характеристики

ПЛИС, являющиеся ключевыми для применений в микромощной

аппаратуре.

зволяют независимо задавать состоя

ние любого выхода в этом режиме. На

выходе может быть состояние лог. 0

или лог. 1, которое было на момент пе

рехода в энергосберегающий режим,

или выход может переходить в высоко

импедансное состояние. Переход в

этот режим и выход из него происхо

дят почти мгновенно – менее чем за

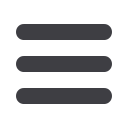

1 мкс. Структурная схема ПЛИС при

ведена на рисунке 1.

Подача активного уровня на вывод

Flash*Freeze является сигналом пере

хода в низкопотребляющее состояние,

который, в зависимости от конфигу

рации, может произойти сразу либо

быть задержан матрицейПЛИС на вре

мя, необходимое для завершения не

отложных операций. Выход из режима

Flash*Freeze может осуществляться как

снятием внешнего сигнала, так и по

инициативе матрицыПЛИС. Посколь

ку потребление КМОП микросхем в

статическом режиме измеряется мик

роваттами, переход в низкопотребля

ющий режим осуществляется снятием

тактового сигнала внутри ПЛИС; при

этом содержимое всех регистров и па

мяти может сохраняться сколь угодно

долго.

Данные о потребляемой мощности

микросхем семейств Igloo в режиме

Flash*Freeze приведены в таблице. Вид

но, что младшие представители семей

ства чрезвычайно экономичны.

О

БЛАСТИ ПРИМЕНЕНИЯ

СВЕРХМАЛОПОТРЕБЛЯЮЩЕЙ

ЛОГИКИ

Как правило, потребление микро

схемне является решающимпри выбо

ре их для использования в том или

ином проекте, поскольку даже при

автономном питании это сводится к

определению требуемой ёмкости ба

тареи. Однако существуют области

применения, где низкая потребляемая

мощность имеет решающее значение.

Причём в последнее время номенкла

тура устройств, требующих микро

мощных ИС, стремительно расширя

ется, в том числе, за счёт удалённых

датчиков, питающиеся от нестандарт

ных источников энергии.

К нестандартным источникам энер

гии можно отнести преобразователи,

использующие естественные механи

ческие колебания, электромагнитные

поля, перепады температуры и слабые

световые потоки. Мощность таких ис

точников незначительна, поэтому тре

буется длительный период накопления

заряда в конденсаторе источника пи

тания перед непродолжительным пе

риодом активной работы датчика. Ис

пользование традиционных ПЛИС, из

готовленных по SRAM технологии, в

таких устройствах невозможно. Во

первых, после включения таких мик

росхем требуется некоторое время на

загрузку конфигурации, т.е. расходует

ся энергия, а полезные операции не

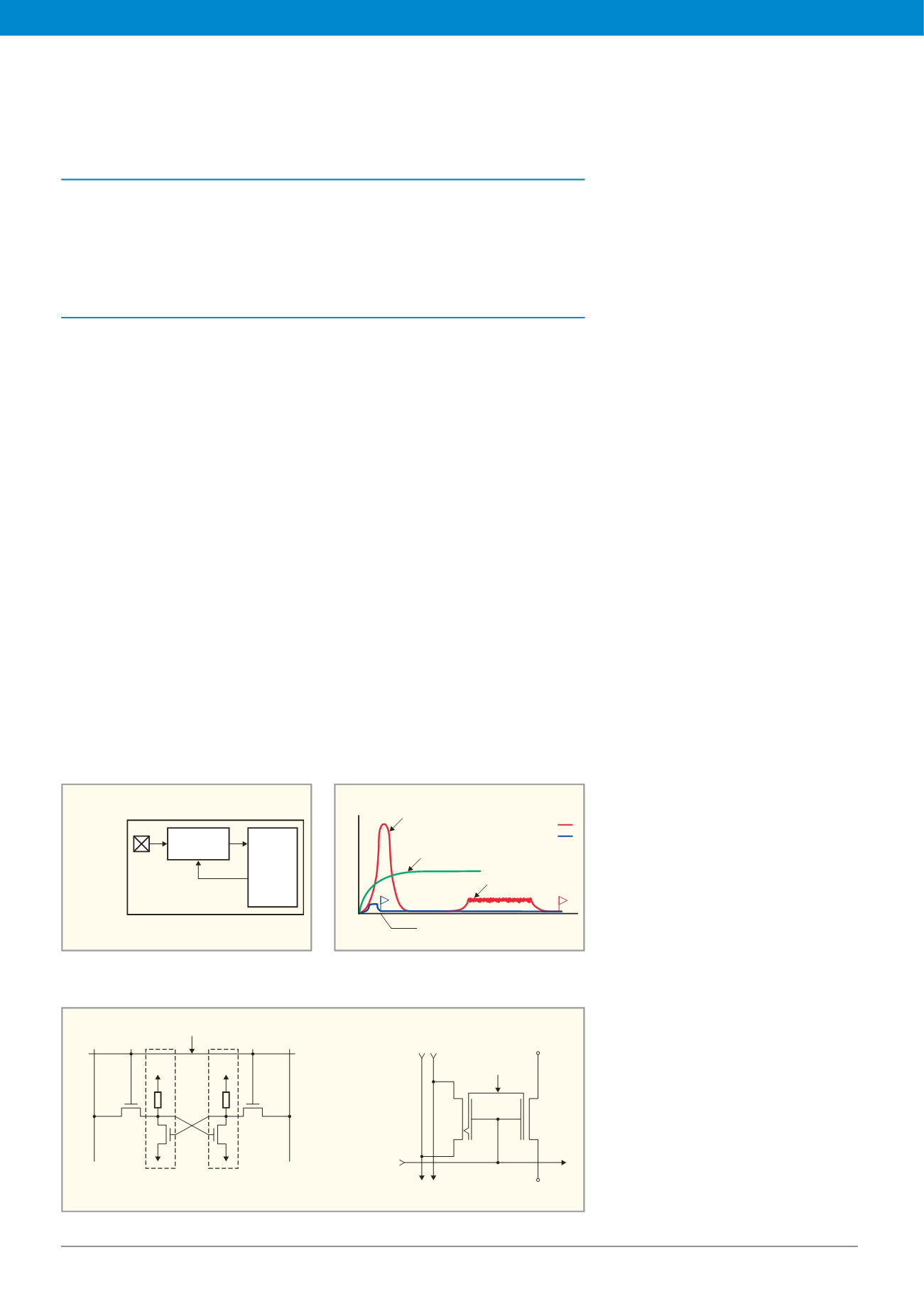

выполняются. Во вторых, при включе

нии таких микросхем происходит рез

кий скачок потребляемого тока (см.

рис. 2).

Это обусловлено тем, что ПЛИС на

основе SRAM хранят информацию о

конфигурации в ячейках памяти типа

SRAM (см. рис. 3). При включении пи

Внешний

вывод

Flash*Freeze

Core

Flash*Freeze

Матрица

ПЛИС

Рис. 1. Структурная схема ПЛИС, оснащённой

режимом Flash*Freeze

Бросок тока

при включении

SRAM (Idds)

Напряжение

питания

SRAM

Flash и Antifuse

Конфигурационный

ток SRAM (Idds)

Время

Готов

Ток

Рис. 2. Временная диаграмма включения

различных типов ПЛИС

Выбор

бита

Выбор

бита

Выход А

Выход А

SRAM

Flash

Выход

Выбор слова

Программирование

Стирание

Считывание

Выбор

слова

Бит

Вход

Flash

Ключ

Vcc

Vcc

Плавающий

затвор

Рис. 3. Функциональные схемы конфигурационных ячеек Flash и SRAM

© СТА-ПРЕСС