# COBPEMEHHAS 6 2008

#### ФОРМУЛА УСПЕХА:

ИДЕИ ЗАКАЗЧИКА, РЕАЛИЗАЦИЯ — ФАСТЕКО

## КОНТРАКТНОЕ ПРОИЗВОДСТВО ЭЛЕКТРОНИКИ

СРЕДНЕЙ И ВЫСШЕЙ КАТЕГОРИИ СЛОЖНОСТИ

- Приоритеты проектам полного цикла производства

- **Комплексные проекты:** от разработки опытного образца до выпуска серийных изделий

- **Лицензии и сертификаты** на производство электронного оборудования

- Планирование поставок готовых изделий по графикам заказчика

- Автоматизированный монтаж печатных плат любой сложности, все типы плат и компонентов.

- Корпусная сборка электронных узлов, крейтов, шкафов и блоков; сборка, тестирование и программирование промышленных компьютеров и контроллеров без ограничений в технологиях.

- Поставка печатных плат любой сложности, соответствие стандартам IPC и ГОСТ. Консультации, доработка.

- 100% комплектование электронными компонентами производственных программ. Регистрация проектов, долгосрочные программы, склад.

- 100% контроль качества: оптический и рентгенконтроль, паспортизация изделий на всех этапах производства, служба контроля качества, ОТК.

- Изготовление лицевых приборных панелей, шильдов, деталей корпусов, радиаторов.

- Изготовление кабелей, жгутов.

- Дизайн-центр по разработке электронного оборудования: от модулей до программноаппаратных комплексов.

№ 6, 2008 Издаётся с 2004 года

**Главный редактор** Александр Майстренко

**Зам. главного редактора** Татьяна Крюк

**Редакционная коллегия** Андрей Данилов, Олег Фёдоров

**Вёрстка**Александр Либков

**Обложка** Дмитрий Юсим

Служба распространения (circul@soel.ru) Мария Кашайкина, Ольга Галыбина

Служба рекламы advert@soel.ru

Издательство «СТА-ПРЕСС» Директор Константин Седов Почтовый адрес: 119313, Москва, а/я 26 Телефон: (495) 232-0087

Факс: (495) 232-1653 Сайт: www.soel.ru E-mail: info@soel.ru

Журнал выходит 9 раз в год

Тираж 10 000 экземпляров Журнал зарегистрирован в Федеральной службе по надзору за соблюдением законодательства в сфере массовых коммуникаций и охране культурного наследия (свидетельство ПИ № ФС77-18792 от 28 октября 2004 года) Свидетельство № 00271-000 о внесении в Реестр надёжных партнеров Торговопромышленной палаты Российской Федерации Цена договорная

Отпечатано: ОАО «Полиграфический комплекс "Пушкинская площадь"» Адрес: 109548, г. Москва, ул. Шоссейная, д. 4д

Перепечатка материалов допускается только с письменного разрешения редакции. Ответственность за содержание рекламы несут рекламодатели. Ответственность за содержание статей несут авторы. Материалы, переданные редакции, не рецензируются и не возвращаются. © СТА-ПРЕСС. 2008

#### Уважаемые читатели!

В этом номере мы обращаемся к наиболее сложным электронным элементам: микропроцессорам и микроконтроллерам.

Бурное развитие электроники - результат совместных усилий специалистов разных стран. Зададимся вопросом: а какое место занимает Россия в этом международном разделении труда? Что наша электронная промышленность может предложить миру? Перечень ограничивается, насколько мне известно, микросхемами для калькуляторов и игрушек. А что могут предложить наши электронные фабрики «оборонке», космосу и авиации? Сообщения о новых российских элементах в нашем журнале были, но было их, к сожалению, немного. По-прежнему в оборонных и авиационно-космических разработках доля импортных комплектующих составляет в ряде случаев более 90%. В основном это как раз высокотехнологичные элементы: микропроцессоры, микроконтроллеры, ПЛИС, системы на кристалле. Эти данные - не новость, они активно обсуждались накануне принятия программы возрождения российской электроники. Но вот программа принята, деньги на неё выделены, и даже были сообщения о приобретении нашими электронными фабриками зарубежного оборудования. Теперь будем ждать сообщений о закупке Пентагоном партии российских суперпроцессоров. Пока это шутка, конечно, но меня всё же не оставляет уверенность в том, что Россия будет не сырьевой страной, а страной высоких технологий, в том числе и в области электроники.

> С уважением, Александр Майстренко

| Market  News from the Russian Market                                                                                      | 4  |

|---------------------------------------------------------------------------------------------------------------------------|----|

| DOLOMANT: Contract Manufacture of Special Purpose Electronics                                                             | 6  |

| Components Microcontrollers AT32UC3 With AVR32 Core (Part 1)                                                              | 10 |

| Introduction in Architecture of Cortex-M3 (Part 1)                                                                        | 18 |

| Modern ICs of 16-Bit Input-Output Expander with Consecutive Interface                                                     | 22 |

| Element Base of PLL: System Approach                                                                                      | 28 |

| Circuit Design  Generators Based on Digital ICs (Part 1)                                                                  | 34 |

| Optoelectronic Drive Circuitry of Power MOSFETs                                                                           | 38 |

| Sine Wave Shaper                                                                                                          | 42 |

| Projects Pumps Drive Controller Nikolay Zaets                                                                             | 46 |

| <b>Design and Simulation</b> CAD TopoR: Creation of Constructive-Technological Restrictions  Sergey Luzin, Oleg Polubasov | 50 |

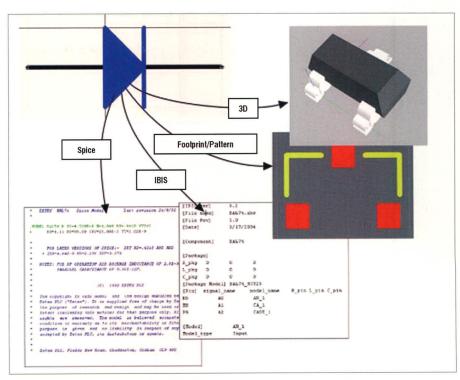

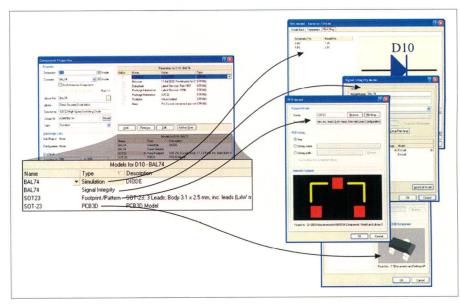

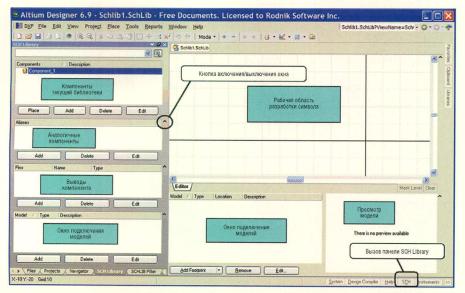

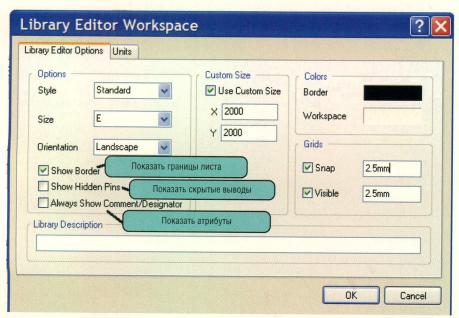

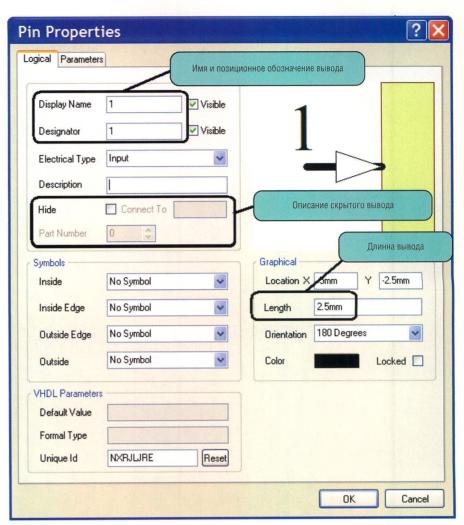

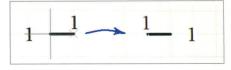

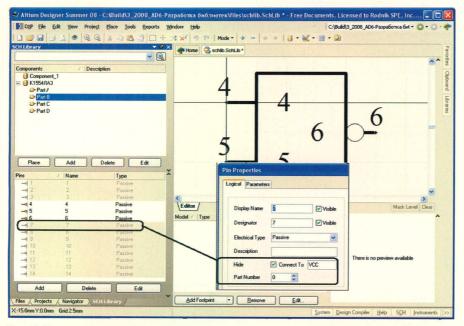

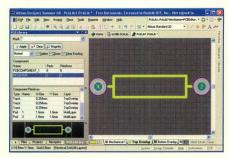

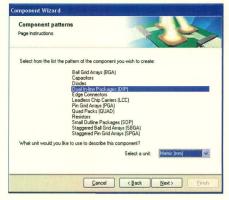

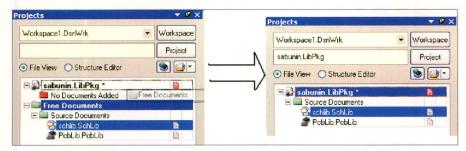

| Altium Designer Summer 08: Development of Components Libraries and Models                                                 | 56 |

| CAD «Elektrik»: Conceptual Bases of Construction and Development                                                          | 64 |

| Practical Course of Design of Digital Devices Based on Xilinx FPGA (Part 15)                                              | 68 |

| Programming Programming Blackfin  Vladimir Bartenev, Maksim Bartenev                                                      | 76 |

#### Рынок

4 Новости российского рынка

6 ДОЛОМАНТ: контрактное производство электроники специального назначения Вадим Лысов

#### Компоненты

10 Микроконтроллеры AT32UC3 с ядром AVR32 (часть 1)

Павел Редькин

18 Введение в архитектуру Cortex-M3 (часть 1)

Павел Вовк

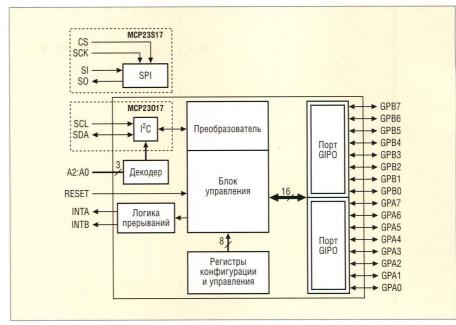

22 Современные интегральные микросхемы 16-разрядного расширителя ввода-вывода с последовательным интерфейсом

Олег Вальпа

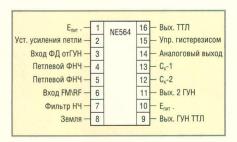

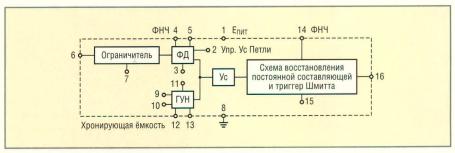

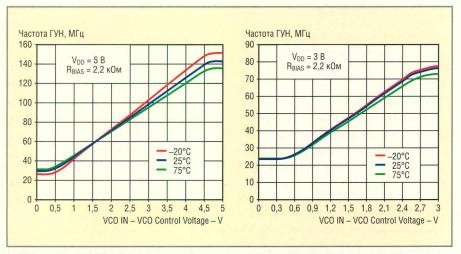

28 Элементная база фазовой автоподстройки: системный подход

Юрий Никитин

### Схемные решения

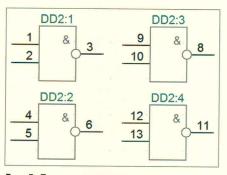

34 Генераторы на основе цифровых микросхем

Сергей Копылов, Дмитрий Николаев, Геннадий Шишкин

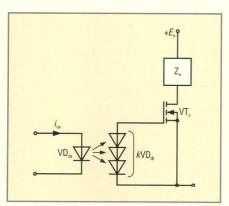

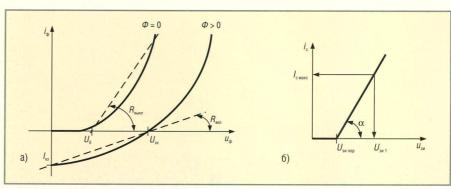

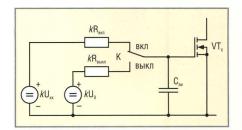

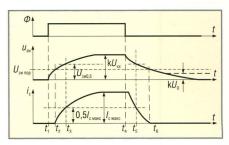

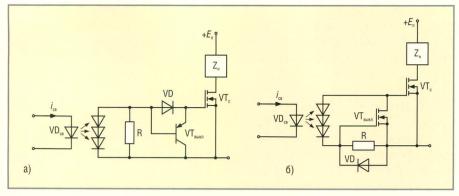

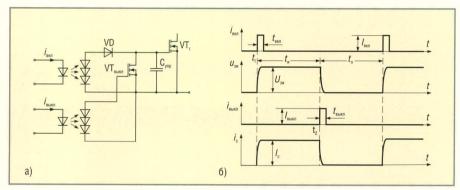

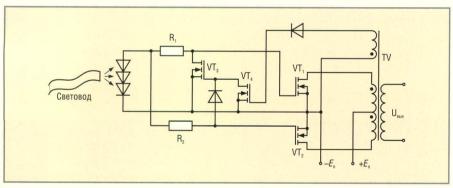

38 Схемы оптоэлектронного управления мощными МОП-транзисторами

Борис Сергеев

42 Формирователь синусоидального напряжения

Олег Дворников

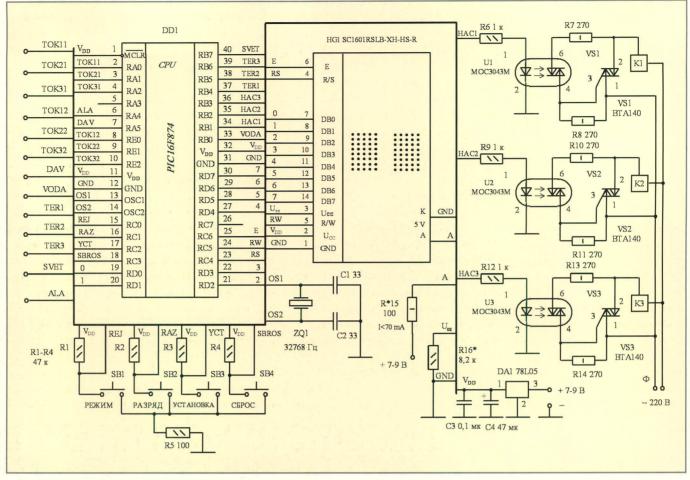

### Проекты

46 Контроллер управления насосами

Николай Заец

## Проектирование и моделирование

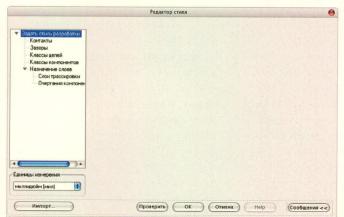

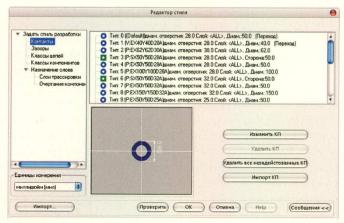

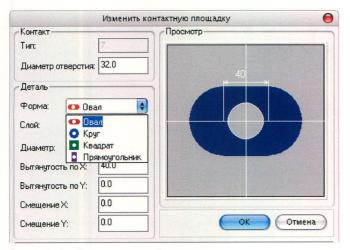

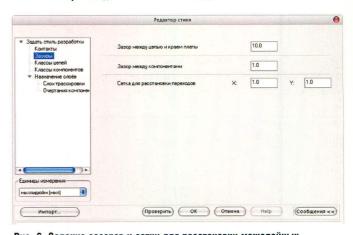

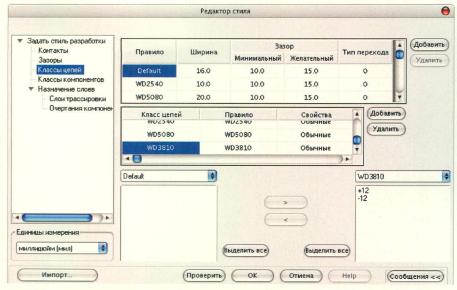

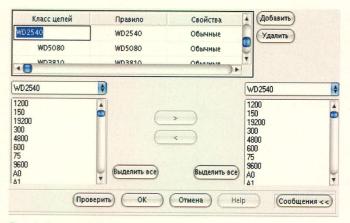

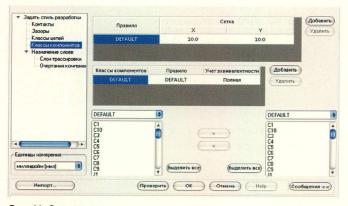

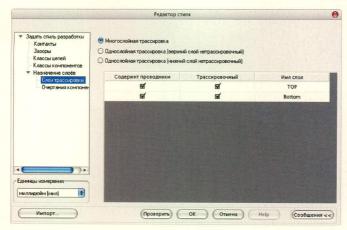

50 САПР ТороR. Задание конструктивно-технологических ограничений

Сергей Лузин, Олег Полубасов

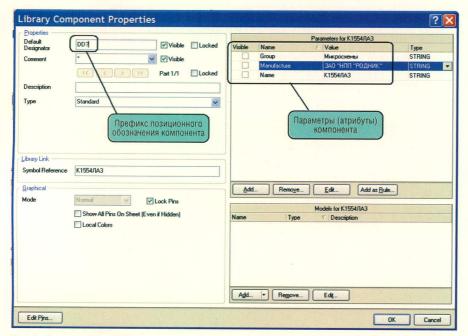

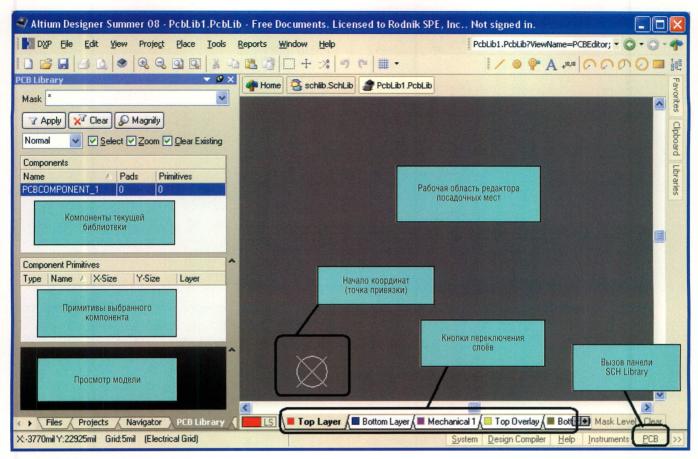

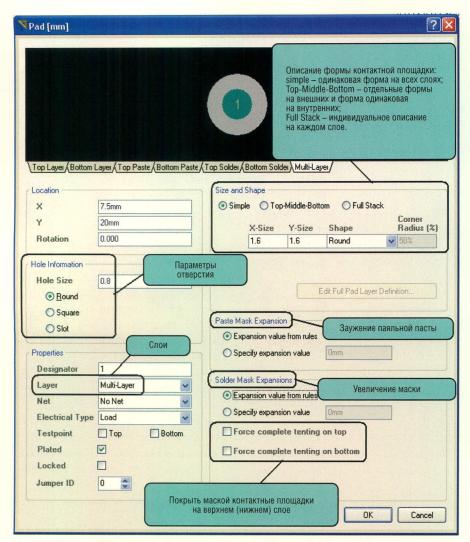

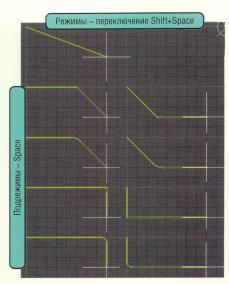

56 Altium Designer Summer 08 – разработка библиотек и моделей компонентов

Алексей Сабунин

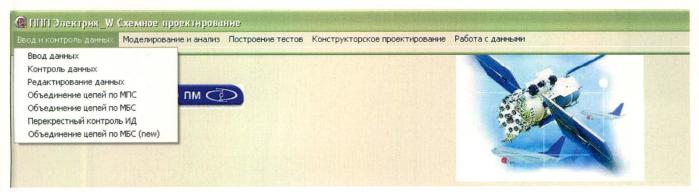

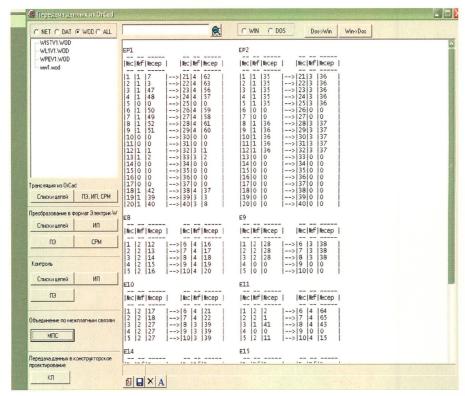

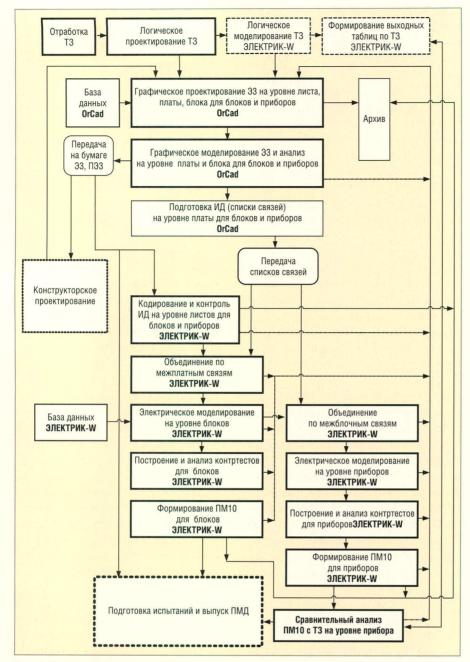

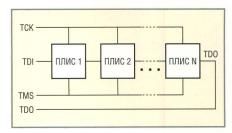

64 Пакет прикладных программ «Электрик» – концептуальные основы построения и развития

Витаутас Зубавичус, Александр Капустин, Станислав Акунович, Марина Салмина,

Ольга Оплетаева, Юрий Леган

68 Практический курс сквозного проектирования цифровых устройств на основе ПЛИС фирмы Xilinx

(часть 15)

Валерий Зотов

### Программирование

76 Программируем ЦПОС Blackfin

Владимир Бартенев, Максим Бартенев

#### Новости российского рынка

#### Компоненты

# Повышающий высоковольтный DC/DC-конвертор от компании austriamicrosystems

Микросхема AS1340 представляет собой микромощный повышающий DC/DC-конвертор с максимальным током внутреннего MOSFET-ключа 1,4 А. При входном напряжении 3,3 В конвертор может

обеспечить выходной ток 30 мА при выходном напряжении 36 В или 100 мА при выходном напряжении 12 В. Напряжение питания микросхемы 2,7...5,5 В, напряжение, подаваемое на МОSFEТ-ключ, 2,7...50 В. Преобразование происходит на фиксированной частоте 1 МГц, высокая частота преобразования позволяет минимизировать внешние компоненты. Функция Power-OK позволяет сигнализировать о более чем 10-% падении напряжения на

выходе конвертора от заданного значения. Отличительной особенностью микросхемы является наличие «спящего» режима с током потребления менее 0,1 мкА. Микросхема выпускается в маленьком корпусе типа TDFN-8 размером 3 × 3 мм и предназначена для работы в схемах питания LCD- и OLED-дисплеев для мобильных устройств.

www.prochip.ru Тел. (495) 232-2522

#### Узлы и модули

# Прецизионные термокомпенсированные кварцевые генераторы ГК202-ТК и ГК203-ТК

ОАО «МОРИОН» (С.-Петербург) разработало новые типы кварцевых термокомпенсированных генераторов – ГК202-ТК и ГК203-ТК. Эти генераторы обеспечивают

уровни стабильности, характерные для термостатированных генераторов (долговременная нестабильность частоты — до  $\pm 1 \times 10^{-7}$ /год и температурная нестабильность частоты до  $\pm 5 \times 10^{-8}$ ), при этом сохраняя такие преимущества термокомпенсированных генераторов, как малое потребление (<100 мВт) и быстрый выход на режим (<0,1 с).

Генераторы выполнены в стандартном корпусе  $36 \times 27$  мм с высотой 12,7...16,0 мм с перспективой уменьшения до 10,0 мм. На сегодня заказчикам предлагаются стандартные частоты 10,0 и 12,8 МГц и варианты исполнения как с 12-B, так и с 5-B питанием.

www.morion.com.ru Тел. (812) 350-7572, (812) 350-9243

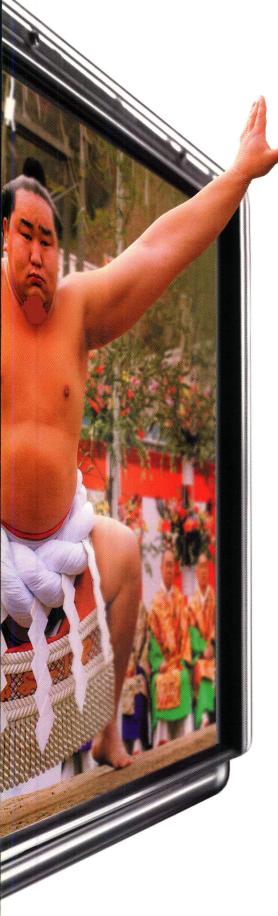

# Новые ЖК-дисплеи AU2025 и CM2225 с высокой яркостью от LiteMax

После выхода Windows Vista в январе 2007 г. всё больше и больше пользователей испытывают потребность в новых ЖК-дисплеях. Широкий формат, короткое время отклика и высокое разрешение стали основными требованиями не только на

рынке коммерческого оборудования, но также в таких промышленных приложениях, как цифровые видеосети и наружные информационные киоски. ЖК-дисплеи LiteMax с высокой яркостью всегда характеризуются новаторскими конструктивными решениями. LiteMax представляет новейшие добавления в ряду ЖК-дисплеев с высокой яркостью с системой задней подсветки на люминесцентных лампах с холодным катодом — AU2025 и CM 2225.

Дисплеи AU2025 и CM2225 созданы на основе плоских панелей компаний AUO и СМО с форматом экранов 16: 9 и совершенно новой конструкцией системы задней подсветки на основе люминесцентных ламп, имеющих яркость 1000 кд/м² и контрастность 700: 1. Обе модели имеют потребляемую мощность 120 Вт. Для представления яркого и высококачественного изображения выбраны панели с высоким разрешением: формат изображения WXGA для AU2025 и WSXGA для CM2225. Обе модели обеспечивают время оптического отклика 8 мс, что позволяет применять дисплеи для показа рекламы и видеороликов с динамичным изображением. Для обеспечения всех приложений заказчиков также был разработан совершенный инвертер LI1222 для панелей CM2225 и AU2025. Инвертер обеспечивает управление яркостью системы задней подсветки от самого низкого уровня до полной яркости, что является чрезвычайно важным для применений в морской аппаратуре, навигационных системах и наружных установках. LiteMax также предоставляет платы управления серии AD для обеспечения многообразных интерфейсных возможностей: VGA, DVI, AV, S-video и Composite. Для дисплеев серий LD и LO также доступны устанавливаемые по заказу защитные стекла и сенсорные экраны.

Технические параметры дисплея LO2025:

- размер экрана, дюймов: 20;

- размер пиксела, мм: 0,325;

- разрешение: 1366 × 768;

- количество отображаемых цветов:

16,2 млн.;

- угол обзора: 160° в обеих плоскостях;

- размеры, мм: 472 × 276,5 × 24,5;

- масса, кг: 2.

Технические параметры дисплея LO2225:

- размер экрана, дюймов: 22;

- размер пиксела, мм: 0,282;

- разрешение: 1680 × 1050;

- количество отображаемых цветов:

16,7 млн.;

- угол обзора: 170° в горизонтальной плоскости, 160° в вертикальной плоскости;

- размеры, мм: 477 × 300 × 26,8;

- масса, кг: 2,5.

www.prosoft.ru Тел. (495) 234-0636

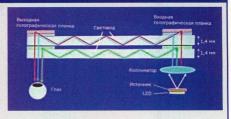

# Новый тюнер Sharp DVB-S2 NIM потребляет всего 1,5 Вт

Sharp расширяет ассортимент тюнеров типа Network Interfaced Module (NIM) для цифрового приёма спутникового телевизионного сигнала высокой чёткости (High Definition-телевидения по спутнику) особо экономичной моделью. Потребляемая мощность нового тюнера DVB-S2NIM типа BS2F7HZ0167 снижена почти на 50% по сравнению с моделью-предшественником (BS2F7HZ0164) — её значение составляет всего 1,5 Вт.

Корпус новой модели идентичен корпусу существующих тюнеров DVB-S2 NIM, т.е. является механически полностью аппаратно совместимым. К тому же BS2F7HZ0167 покрывает типичный для спутникового приёма частотный диапазон

#### Новости российского рынка

950...2150 МГц и пригоден для приёма как HDTV-сигналов по стандарту DVB-S2, так и сигналов по стандарту DVB-S. Новый тюнер BS2F7HZ0167 отличается выдающимися техническими параметрами: коэффициент шума составляет всего 6 дБ (тип.), а фазовые шумы всего около –80 дБ/Гц (тип.) при смещении 10 кГц. Также новый DVB-S2NIM имеет отличные показатели чувствительности сигнального входа, динамики и избирательности.

Блок NIM-демодулятора BS2F7HZ0167 несёт в своём составе новейший чип типа STV0903, который обеспечивает 8PSK/QPSK-демодуляцию и выдаёт цифровой 8-разрядный поток данных для последующей обработки сигналов.

У разработчиков, применяющих в своих проектах ресивер с отдельным демодулятором, появилась возможность использовать современную интегрированную тех-

нологию спутникового HDTV-приёма от Sharp. Данная технология предусматривает применение встроенного в ресивер QPSK-демодулятора. Пользователям, самостоятельно разрабатывающим ресивер с отдельным демодулятором, не придётся отказываться от современнейшей технологии спутникового HDTV-приёма Sharp.

Модели BS2S7VZ0604 и BS2S7HZ0604 из новой серии DVB-S2-тюнеров позиционируются на рынке как СВЧ-фронтенды соответственно для вертикальной и горизонтальной установки на плату. Они обеспечивают такой же высококачественный приём, как и новые тюнеры DVB-S2NIM. Эти так называемые «RF-Only-тюнеры» базируются на технологии Sharp с превосходными радиочастотными ИС собственной разработки.

Партнёр компании ПРОСОФТ, Sharp располагает обширным ноу-хау по разработке и производству приёмных компо-

нентов. К слову, в 2005 г. Sharp одним из первых вышел на европейский рынок с тюнером DVB-S2 для приёма HDTV-сигналов, вещаемых со спутника. Обширный ассортимент включает в себя более 40 тюнеров цифрового телевизионного приёма через спутник, по кабелю и по эфиру, обеспечивает соответствующее решение практически для любого устройства. Новый тюнер DVB-S2 NIM типа BS2F7HZ0167, как и все компоненты тюнеров Sharp, с мая 2008 г. можно приобрести в компании ПРОСОФТ.

www.prochip.ru Тел. (495) 232-2522

#### Приборы

#### Быстро, точно, удобно – новая серия осциллографов LeCroy

Компания LeCroy объявила о выпуске новой серии осциллографов. Серия носит название WavePro 7 Zi. Она является ответом на постоянно возрастающие требования к характеристикам приборов и приходит на смену сразу двум линейкам приборов LeCroy: WavePro и WaveMaster.

В серии представлены пять моделей осциллографов общего применения и четыре модели анализаторов сигналов последовательных данных с полосами пропускания от 1,5 до 6 ГГц и частотами дискретизации в реальном времени 20 ГГц на канал и 40 ГГц в режиме объединения каналов. При этом максимально возможный объём памяти на канал составляет до 256 Мб. В осциллографах использована принципиально новая потоковая архитектура передачи данных X-Stream II, которая обеспечивает быстродействие в 10 – 20 раз быстрее

при работе с большими массивами данных, чем у аналогичных приборов других производителей. Для более удобного наблюдения сигналов WavePro 7 Zi имеет широкоформатный дисплей 39 см, что является самым большим осциллографическим экраном на сегодняшний день.

Помимо ранее использовавшейся сегментированной развёртки, программного алгоритма поиска WaveScan и режима «быстрого отображения» WaveStream, в осциллографах WavePro 7 Zi применена система TriggerScan. TriggerScan является программно-аппаратным решением, использующим специальную высокоскоростную микросхему предзапуска и позволяет проводить последовательное сканирование сигнала по различным комбинациям условий запуска.

Как и все осциллографы от LeCroy, новая серия обладает широким набором инструментов для анализа сигналов: программных (измерения, математика, графический и статистический анализ, интеграция с программными пакетами типа MatLab) и аппаратных (все виды пробников, включая логические, а также синхронизация и декодирование низкоскоростных и высокоскоростных потоков последовательных данных).

www.prist.ru Тел. (49<mark>5</mark>) 777-5591

#### Программирование

#### Отладочные средства компании «Миландр»

Компания ЗАО «ПКК Миландр» начала производство и продажу отладочных средств для первого российского микроконтроллера с САN-интерфейсом. В состав отладочного комплекта входят: отладочная плата, программатор, необходимые интерфейсные кабели, несколько образцов данного микроконтроллера, а также отладочная сре-

да собственной разработки, которая существенно облегчает процесс создания и отладки программного обеспечения для всех контроллеров серий 1886. Кроме CAN 2.0b интерфейса (стандарта ISO 11898, проходившего тестирование в Германии), в состав данного контроллера входят: 10-разрядный 8-канальный АЦП, интерфейсы LIN, USART, 8 × 8 аппаратный умножитель, память программ (4К × 16), память данных (902 байта),

несколько таймеров; наличие Sleep-режима и т.д. Рабочий температурный диапазон микросхемы (в металлокерамическом корпусе) от –60 до +125°С. В продолжение серии 1886 сейчас разрабатываются ещё два микроконтроллера: 1886ВЕ6У (с АЦП (12 разрядов) и ЦАП) и 1886ВЕ7У (с пониженным энергопотреблением). Образцы данных схем ожидаются в сентябре-октябре 2008 г.

www.milandr.ru Тел. (495) 739-0282

# ДОЛОМАНТ: контрактное производство электроники специального назначения

#### Вадим Лысов (Москва)

Высокотехнологичная, с мощными производственными и кадровыми ресурсами коммерческая компания на рынке контрактной разработки и производства в лицензируемых отраслях – явление пока уникальное в нашей стране. Бизнес-процесс исполнения электронных проектов предприятий, работающих традиционо в сфере гособоронзаказов и под патронажем Ростехнадзора выделен в чистом, коммерческом виде для открытого сотрудничества, парнёрства и конкуренции с государственными предприятиями электронной отрасли. Если история развития и весь мировой опыт наиболее развитых «электронных» стран, задающих тон в гражданских и специальных технологиях и разработках в области электроники, применим к России, в недалеком будущем этот успешный, но единичный пока проект станет просто первым среди многих.

Рынок контрактного производства электроники в России растёт быстрыми темпами, более чем на 25% в год. Принятие федеральных целевых программ обеспечивает государственную поддержку электронной промышленности. Конкуренция, активное сотрудничество и соперничество на поле важнейших государственных заказов частных компаний и государственных предприятий максимально полно отвечают поставленным задачам модернизации электронной промышленности и восстановлению безопасности этой стратегической отрасли.

Сочетание всех этих факторов способствовало появлению в России проекта создания независимого бизнес-направления «Контрактное производство электроники для исполнения лицензируемых проектов» под торговой маркой ДОЛОМАНТ.

Компания ДОЛОМАНТ предоставляет услуги современного высокотехнологичного комплексного производства предприятиям, работающим по специальным условиям и выполняющим лицензируемые государственные заказы, включая гособоронзаказ.

Уникальность проекта «лицензируемого контрактного производства» заключается в эффективном объединении передовых достижений независимых контрактных производителей изделий электроники общего назначения и заводов, традиционно выполняющих специальные государственные заказы. Сопряжение лучших качеств управления, отчётности, технологий контроля качества каждого этапа реализации, дисциплины производства плюс отлаженный интерфейс в поле принятых стандартов для исполнителей лицензируемых заказов — отличительные черты нового направления.

Отмечая успех идеи, доказавшей право на жизнь и дальнейшее развитие, нужно отдавать отчёт в том, что очень многое будет зависеть от промышленной политики соответствующих государственных структур. В любом случае уже в ближайшее время уникальность положения «специального контрактного производителя» должна измениться, и это стоит только приветствовать.

Прогнозируется, что такое положение верно только на ограниченный период времени и означает только «первые из грядущих». Для стран с высоким уровнем технологий и объёмов электронной промышленности характерно, что именно частные компании, независимые производители являются инициаторами модернизации технологий, лидерами в разработках и построении современных процессов. При этом государственные органы, отвечающие за безопасность ключевой электронной промышленности, опираются в первую очередь на такие компании, помогая им законами, экономическими преференциями, распределе-

нием бюджетных, стратегических заказов и антимонопольным регулированием.

Законы природы не имеют границ, законы же экономического развития локализованы и имеют свою точную прописку по эпохам и государственной принадлежности. Выходя на отечественный рынок с новым бизнеспроектом, мы надеялись в первую очередь добиться эффективности предложенных решений реализации лицензируемых (государственных, бюджетных) заказов.

В долгосрочном, стратегическом плане ДОЛОМАНТ поставил задачу быть в группе лидирующих инновационных предприятий отрасли, занимая собственную нишу пионера технологий и дисциплины производства, соответствовать понятию интеллектуального отечественного производителя электроники специального назначения. Для достижения заявленных целей ДОЛОМАНТ обладает необходимым опытом, сбалансированным капиталом квалифицированных кадров, оснащённого передовыми технологиями производства и, главное, волей для достижения поставленных целей.

Основные направления деятельности ДОЛОМАНТ:

- изделия собственной разработки, предназначенные для ответственных применений;

- поставка электронной компонентной базы в статусе «второго поставшика»:

- контрактные разработки и производство полного цикла модулей, узлов, блоков в соответствии с лицензионными условиями (поставка с приёмкой «ВП», лицензии Ростехнадзора, Роспрома, ФСБ, система менеджмента качества, сертифицированная в СДС «Военный регистр», Свидетельство об аттестации второго поставщика).

Для осуществления указанных видов деятельности фирма имеет полный пакет разрешительных документов (лицензий, свидетельств, сертификатов, решений и пр.), выданных Минобороны, Роспромом, Ростехнадзором, ФСБ и пр.

Дизайн-центр предприятия разрабатывает электронное оборудование для жёстких условий эксплуатации. Уровень разрабатываемых изделий – от модулей до программно-аппаратных комплексов. Возможности центра:

- проработка технических требований, разработка технического задания и эскизного проекта;

- разработка схемотехнических решений;

- трассировка печатных плат любой сложности;

- конструирование механических деталей, узлов, корпусов и кабелей;

- разработка системного ПО, в том числе: операционные системы, BIOS, драйверы, коммуникационные протоколы;

- разработка прикладного ПО;

- любые виды испытаний: вибро-механика, климатика, ЭМС, радиационная стойкость и др.;

- производство макетных образцов;

- выпуск конструкторской документации по ЕСКД.

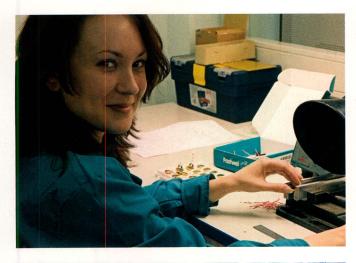

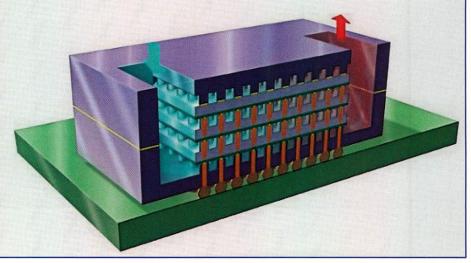

Производственные мощности предприятия включают:

• монтажный цех, выполняющий пайку любой сложности на автоматических линиях (SMD-компоненты) и селективную пайку (DIP-компоненты); возможны свинцовая и бессвинцовая технология пайки. Есть вспомогательный цех ручного монтажа; автоматическая оптическая инспекция и паспорти-

зация изделий с момента монтажа; рентген-контроль пайки, восстановление компонентов ВGA. Оборудование позволяет производить весь спектр электронных изделий: от простейших модулей с 10 – 30 компонентами «на борту» до сложнейших процессорных модулей. Производственная мощность до 100 000 модулей в месяц;

механический цех, выполняющий сборку шкафов, блоков, узлов; контакт накруткой, пайкой, зажимом; изготовление кабелей, изготовление и доработку панелей приборов, радиаторов, элементов корпусов.

Все производственные программы предприятия по изготовлению изделий собственной разработки и контрактной сборки полностью комплектуются электронными компонентами. Возможна поставка высококачественных печатных плат любого уровня сложности, отвечающих международным стандартам ІРС и российским ГОСТам, с заводов в Корее и Финляндии.

На предприятии действует система инспекции качества, включающая в себя службу контроля качества, ОТК и контроль качества военным представительством. Система инспекции качества позволила получить 99,9% годной продукции при серийном изготовлении модулей повышенной сложности.

В качестве второго поставщика предприятие поставляет предприятиям ОПК 400 000 наименований изделий электронной компонентной базы от 63 иностранных производителей.

На предприятии внедрена система маркетинга непрерывного управления заказами и технической поддержки во время исполнения заказов и в период их эксплуатации.

Максимальный эффект от кооперации достигается с компаниями:

рыночно распоряжающимися своим проектом выпуска сложной и/или высокотехнологичной немассовой электроники всех отраслей применения;

- имеющими жёсткие требования на обязательную успешную реализацию проекта (например, государственный заказ);

- имеющими долгосрочные перспективы или однократный, но крупный проект, готовыми к сотрудничеству в области перехода на современные технологии;

- передающими на аутсорсинг полный комплекс работ контрактному производителю. Приоритеты – проектным решениям, охватывающим весь комплекс имеющихся инжиниринг-производственных возможностей контрактного производителя;

- планирующими свой бизнес на каждом этапе его осуществления: от опытных образцов и планомерной закупки комплектующих до выхода на график выпуска готовых серийных партий;

- умеющими считать стоимость проектов во всей их полноте, оценивающими эффективность выпуска конечного продукта и соотносящи-

ми реальную стоимость с потенциальными рисками.

Развитие производственной базы в 2008 г. предполагает двух-/трёхкратное увеличение мощности и возможностей цеха монтажа, переход на уверенную работу с современными компонентами в корпусах размеров 0201, дооснащение оборудованием цехов мехобработки и изготовления передних панелей, радиаторов, элементов корпусов, расширение участков сборки промышленных компьютеров, блоков, узлов, стоек и шкафов. Продол-

жится отладка процедур обработки заказов в соответствии с принятыми стандартами предприятия, расширение ассортимента услуг производства и разработок, согласование технологического и документального интерфейса взаимодействия с предприятиями, работающими в области выполнения государственных заказов. Также планируется выработать предложения по оценке качества модулей, изготовленных по смешанной технологии (традиционные компоненты отечественного производства и закупаемые

по импорту с бессвинцовыми покрытиями, печатные платы с покрытием HASL и IMG, пасты, флюсы, лаки) на весь эксплуатационный период.

На сегодняшний день бизнес-проект ДОЛОМАНТ уже имеет в активе десятки успешных реализаций комплексных заказов, проведённых под контролем Ростехнадзора и с военной приёмкой. ДОЛОМАНТ продолжит активную работу, направленную на решение проектных, комплексных задач в области производства электроники специального назначения.

#### ЗАО «НПФ «ДОЛОМАНТ» ПРИГЛАШАЕТ К СОТРУДНИЧЕСТВУ И ОСУЩЕСТВЛЯЕТ:

#### поставку 🗠

электронных компонентов в качестве второго поставщика (номенклатура порядка 400 тыс. наименований более 60 зарубежных производителей) при сотрудничестве с группой компаний ПРОСОФТ

#### производство 🗵

промышленных и встраиваемых компьютеров (в форматах Compact PCI, VME, EPIC, 3,5", PC/104, MicroPC, AT96, PICMG, Mini-ITX, ATX), плат для монтажа на DIN-рейку, а также каркасов, шлейфов, кабелей и аксессуаров, предназначенных для работы в жёстких условиях эксплуатации с военной приёмкой

#### разработку 🖈

программных и аппаратных средств по техническому заданию заказчика под контролем военного представительства

#### контрактную сборку 🗲

изделий по конструкторской документации заказчика, включая изготовление печатных плат, поверхностный монтаж и тестирование электронных модулей, изготовление механических деталей корпусов и передних панелей под контролем военного представительства

Производственное высокоавтоматизированное оборудование для поверхностного монтажа электронных модулей 3AO «НПФ«Доломант» соответствует уровню требований мировых производителей. Оборудование адаптировано к использованию бессвинцовой технологии, позволяет производить автоматическую разбраковку и рентгеновский контроль качества пайки.

#### ЗАО «НПФ «ДОЛОМАНТ»

имеет лицензии на разработку и производство электронных средств для вооружения и военной техники и атомных электростанций, свидетельство об аттестации второго поставщика, а также систему менеджмента качества, сертифицированную в системе «Военный регистр» на соответствие ГОСТ Р ИСО 9001 и ГОСТ РВ 15.002.

> 117437, Москва, ул. Профсоюзная, д. 108 Тел./факс: (495) 232-20-33 E-mail: info@dolomant.ru Web: www.dolomant.ru

Реклама

WWW.SOEL.RU

# Микроконтроллеры AT32UC3 с ядром AVR32

(часть 1)

#### Павел Редькин (г. Ульяновск)

В настоящее время у разработчиков электронной аппаратуры весьма популярны встраиваемые микроконтроллеры с 8-разрядным процессорным ядром архитектуры AVR фирмы Atmel, которая предлагает обширный модельный ряд этих устройств, включающий несколько подсемейств. Однако постоянно растущие требования к производительности, функциональной насыщенности и возможностям периферии, быстродействию подсистем ввода-вывода заставляют разработчиков использовать МК с 16- и 32-разрядными процессорными ядрами.

В начале 2006 г. компания Atmel анонсировала новое 32-разрядное процессорное ядро AVR32 и первый МК на его основе – AT32AP7000. В настоящее время на базе ядра AVR32 выпускается уже два семейства МК.

Предлагаемая статья посвящена одному из этих семейств – «классическим» микроконтроллерам AT32UC3 (аббревиатура UC означает microcontroller). В первой части статьи приводится перечень устройств AT32UC3, описание их архитектуры, программной модели и организации памяти.

Во второй части содержится информация о составе и характеристиках встроенной периферии AT32UC3.

В третьей части рассказывается о входящих в состав AT32UC3 модулях тестирования и отладки, а также о существующих инструментальных средствах разработки, отладки и программирования пользовательских приложений на базе этих МК.

#### Семейства МК с ядром AVR32

По оценкам экспертов, МК с ядром AVR32 выигрывает по производительности и энергопотреблению у большинства приборов, ориентированных на рынок мультимедийных приложений, в том числе, с архитектурой ARM. Последнее весьма существенно, поскольку в настоящее время архитектура ARM, поддерживаемая ведущими производителями, стала фактическим стандартом в сегменте 16- и 32-разрядных МК и ПЛИС.

Так, например, алгоритм iDCT (инверсное дискретное косинусное преобразование) платформа с ядром AVR32 может выполнять на 35% быстрее, чем ядро ARM11. При выполнении стандартных тестов на производительность EEMBC архитектура AVR32 также демонстрирует ощутимое превосходство, причём не только над архитектурой ARM7, но и над архитектурами ARM9 и ARM11 [1].

Необходимо отметить, что удельная производительность ядра AVR32 (относительно его тактовой часты), выраженная в DMIPS/МГц, при выполнении программы из статического ОЗУ (SRAM) и флэш-памяти имеет значение, существенно большее единицы (типичное – 1,38), в то время как для ядер ARM7 и ARM9 эта величина равна или меньше единицы.

Разработчики AVR32 подчёркивают оригинальные особенности новой архитектуры:

- команды обращения к памяти (записи/чтения) могут оперировать со всеми типами данных: байтами, полусловами, словами и двойными словами;

- набор команд оптимизирован для работы с распространёнными алгоритмами блочного шифрования Blowfish и Triple-DES;

- ядро имеет семь стадий конвейера (три стадии в «облегчённой» архитектуре AVR32 – AT32UC3) и поддерживает одновременное выполнение не связанных друг с другом операций с изменением их последовательности, которая задаётся

программой. Для экономии тактовых циклов предусмотрена функция пересылки результата текущей операции на предыдущие ступени конвейера на случай, если следующая команда использует этот результат;

- поддерживаемые архитектурой операции множественного доступа к данным позволяют увеличить скорость выполнения программы в четыре раза;

- аппаратная функция прогнозирования переходов (ветвлений) в AVR32 минимизирует потери тактовых циклов при переходах с помощью команд rjmp, rcall и if (из набора Java);

- при разработке системы команд максимальное внимание уделено плотности результирующего кода при выполнении типичных операций в мультимедиа-приложениях;

- в составе системы команд имеются дополнительные команды для операционных систем (ОС). Обеспечена максимальная совместимость платформы с ОС Linux, которая может полноценно использовать встроенный блок управления памятью (ММU), а также привилегированный/пользовательский режимы работы ядра AVR32;

- гибкая система управления энергопотреблением МК на 80% реализована за счёт системы команд процессорного ядра AVR32 и на 20% – на этапе реализации МК в «железе». Последнее достигается за счёт размещения устройств хранения данных в непосредственной близости к ядру.

На момент написания этой статьи все предлагаемые компанией Atmel устройства с архитектурой AVR32 можно было отнести к одному из двух семейств:

базовое семейство АТ32АР (процессорное ядро AVR32A) – высокопроизводительные приборы (тактовая частота ЦПУ до 150 МГц) с мощной и разнообразной периферией (интерфейсы видеокамеры, графичес-

Таблица 1. Сравнительные данные по току потребления МК различных производителей

| Устройство (производитель)                                                                                                                                              | Напряжение питания: ток потребления в активном режиме                                                                                                                                       | Напряжение питания: ток потребления в<br>статическом режиме                                                                                   | Примечания  МК с ядром ARM7 (информация с сайта: www.analog.com)             |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|

| ADuC7128/7129 (Analog Devices)                                                                                                                                          | 3,0 В: 42 мА (ЦПУ выполняет программу из флэш-памяти, тактовая частота 42 МГц, всё периферийное тактирование активно)                                                                       | 3,0 В: 300 мкА (ЦПУ находится в статическом режиме)                                                                                           |                                                                              |  |

| AT32UC3A0512/1512/0256/1256/0128/1128<br>(Atmel)                                                                                                                        | 3,3 В: 37 мА (ЦПУ выполняет программу из флэш-памяти, тактовая частота 60 МГц вырабатывается ФАПЧ, всё периферийное тактирование активно, встроенный стабилизатор 1,8 В включен и нагружен) | 3,3 В: 25 мкА (ЦПУ находится в статическом режиме, всё периферийное тактирование неактивно, встроенный стабилизатор 1,8 В включен и нагружен) | MK с ядром AVR32<br>(информация с сайтов:<br>www.atmel.com,<br>www.avr32.ru) |  |

| 3,3 В: 44 мА (ЦПУ выполняет программу из флэш-памяти, тактовая частота 50 МГц, всё периферийное тактирование активно, встроенный стабилизатор 1,8 В включен и нагружен) |                                                                                                                                                                                             | 3,3 В: 26 мкА (ЦПУ находится в статическом режиме, всё периферийное тактирование неактивно, встроенный стабилизатор 1,8 В включен и нагружен) | MK с ядром ARM7.<br>(информация с сайта:<br>www.atmel.com)                   |  |

| LPC2141/2142/2144/2146/2148 (NXP)                                                                                                                                       | 3,3 В: 57 мА (ЦПУ выполняет программу из флэш-памяти, тактовая частота 60 МГц, всё периферийное тактирование неактивно, кроме USB)                                                          | 3,3 В: 40 мкА (ЦПУ находится в статическом режиме, всё периферийное тактирование неактивно)                                                   | MK с ядром ARM7                                                              |  |

| LPC2377/2378 (NXP)                                                                                                                                                      | 3,3 В: 92 мА (ЦПУ выполняет программу из флэш-памяти, тактовая частота 72 МГц, всё периферийное тактирование активно)                                                                       | 3,3 В: 150 мкА (ЦПУ находится в статическом режиме)                                                                                           | (информация с сайта:<br>www.standardics.nxp.com)                             |  |

| TMS470R1B512 (Texas Instruments)                                                                                                                                        | 3,6 В: 55 мА, 2,05 В: 125 мА (ЦПУ выполняет программу из флэш-памяти, тактовая частота 60 МГц, всё периферийное тактирование активно)                                                       | 3,6 В: 20 мкА,2,05 В: 2 мА (ЦПУ находится в статическом режиме)                                                                               | MK с ядром ARM7<br>(информация с сайта:<br>www.ti.com)                       |  |

кого ЖКИ, звукового ЦАП, SD/MMC-карт памяти, графического сопроцессора, аппаратного ускорителя JAVA и т.д.). Недостатком этих устройств является отсутствие встроенной флэш-памяти программ, что несколько затрудняет или ограничивает их использование в ряде приложений;

• семейство AT32UC3 («облегченное» процессорное ядро AVR32UC). Особенность этих устройств - наличие встроенной флэш-памяти на кристалле. По этой причине МК AT32UC3 могут использоваться без какой-либо дополнительной «обвязки», т.е. являются самодостаточными микроконтроллерами. Однако их максимальная производительность существенно ниже, чем у приборов семейства АТЗ2АР, поскольку тактовая частота ИПУ не превышает 66 МГц. Кроме того, по сравнению с АТ32АР, возможности процессорного ядра скромнее, а набор встроенной периферии значительно беднее. Несмотря на это, МК семейства АТ32UC3 представляются весьма перспективными устройствами, заслуживающими внимания разработчиков.

Старшие представители МК семейства AT32UC3 обеспечивают производительность на уровне 80 DMIPS, потребляя в активном режиме ток около 40 мА при питании от напряжения 3,3 В. Удельная потребляемая мощность этих устройств составляет 1,65 мВт/DMIPS (0,6 мА/МГц), что, по заявлению производителя, примерно в четыре раза ниже, чем у аналогов, построенных по другой архитектуре [2].

Для сравнения в таблице 1 показаны значения потребляемого тока для нескольких сходных по своим возможностям МК различных производителей при одинаковых или близких внешних условиях. Как видно из таблицы 1, разница в энергопотреблении МК с ядром AVR32 и конкурирующих МК в активном режиме хотя и не достигает четырёхкратной величины, но, тем не менее, весьма значительна.

По утверждению производителя, использование ядра AT32UC3 обеспечивает размер откомпилированного кода на 5...20% меньший, чем размер откомпилированного кода для ядра с архитектурой ARM, использующего систему команд Thumb. Для системы команд ARM выигрыш в размере откомпилированного кода достигает 30...50%.

Фирма Atmel также объявила, что ядро МК АТ32UC3 является первым ядром в отрасли, в которое интегрирована статическая память с интерфейсом прямой связи с процессором и

однотактным чтением/записью, что позволяет ускорить исполнение кода при меньшем энергопотреблении.

В отношении встроенной периферии AT32UC3 заметим, что многие периферийные модули МК этого семейства по своей архитектуре и пользовательским интерфейсам практически идентичны периферийным модулям МК выпускаемого фирмой Atmel семейства AT91SAM7, которое широко известно разработчикам. Это обстоятельство, несомненно, упростит освоение AT32UC3.

Перечень устройств архитектуры AT32UC3 (подсемейств AT32UC3A и AT32UC3B) приводится соответственно в таблицах 2 и 3. Часть набора встроенной периферии, одинаковая для всех устройств AT32UC3A, в таблице 2 не указана, а перечислена ниже в тексте.

Как можно видеть из таблиц, МК подсемейства AT32UC3B предназначены для простых приложений, а МК

Таблица 2. Микроконтроллеры подсемейства AT32UC3A

| Устройство   | Флэш-память, Кб | SRAM, Kó | Интерфейс внешней шины | EthernetMAC | Корпус            |

|--------------|-----------------|----------|------------------------|-------------|-------------------|

| AT32UC3A0512 | 512             | 64       |                        | +           | 144-выводной LQFP |

| AT32UC3A1512 | 512             | 64       | -                      | +           | 100-выводной TQFP |

| AT32UC3A0256 | 256             | 64       |                        | +           | 144-выводной LQFP |

| AT32UC3A1256 | 256             | 64       | -                      | +           | 100-выводной TQFP |

| AT32UC3A0128 | 128             | 32       | +                      | +           | 144-выводной LQFP |

| AT32UC3A1128 | 128             | 32       | -                      | +           | 100-выводной TQFP |

Таблица 3. Микроконтроллеры подсемейства AT32UC3B

| Устройство   | Флэш-память, Кб | SRAM | USART | SSC | ADC | OSC | Конфигурация USB      | Корпус               |

|--------------|-----------------|------|-------|-----|-----|-----|-----------------------|----------------------|

| AT32UC3B0256 | 256             | 32ĸ  | 3     | +   | 8   | 2   | Минихост + устройство | 64-выводной TQFP/QFN |

| AT32UC3B1256 | 256             | 32к  | 2     | -   | 6   | 1   | Устройство            | 48-выводной TQFP/QFN |

| AT32UC3B0128 | 128             | 32к  | 3     | +   | 8   | 2   | Минихост + устройство | 64-выводной TQFP/QFN |

| AT32UC3B1128 | 128             | 32к  | 2     | _   | 6   | 1   | Устройство            | 48-выводной TQFP/QFN |

| AT32UC3B064  | 64              | 16ĸ  | 3     | +   | 8   | 2   | Минихост + устройство | 64-выводной TQFP/QFN |

| AT32UC3B164  | 64              | 16ĸ  | 2     | -   | 6   | 1   | Устройство            | 48-выводной TQFP/QFN |

подсемейства AT32UC3A – для более сложных. Следует отметить, что Atmel планирует в перспективе выпуск подсемейств AT32UC3C, AT32UC3D и AT32UC3E [2].

Устройства подсемейства AT32UC3A имеют следующие типовые характеристики [3, 5]:

- Высокоэффективное 32-разрядное процессорное ядро с оригинальной архитектурой AVR32 и следующими особенностями:

- компактная система команд RISC, выполняющихся за один цикл, включая команды DSP;

- команды «чтение-модификациязапись» и команды манипуляций с битами;

- тактовая частота до 66 МГц при удельной производительности 1,38 DMIPS/МГц;

- производительность 83 DMIPS при выполнении программы из флэш-памяти с тактовой частотой 66 МГц (1 цикл ожидания);

- производительность 45 DMIPS при выполнении программы из флэш-памяти с тактовой частотой 33 МГц (0 циклов ожидания);

- модуль защиты памяти (MPU);

- Мультииерархическая шинная система со следующими особенностями:

- высокоэффективный обмен данными по отдельным шинам для повышения производительности;

- 15 каналов DMA для автоматической передачи данных;

- Встроенная высокоскоростная флэш-память со следующими особенностями:

- объём от 512 до 128 Кб;

- доступ за один тактовый цикл на тактовой частоте до 30 МГц;

- буфер выборки с упреждением для оптимизации выполнения команд на максимальной тактовой частоте:

- время программирования страницы 4 мс, время стирания всего кристалла 8 мс;

- 100 000 циклов записи, 15-летний срок сохранности данных;

- ключи защиты памяти и задаваемые пользователем области конфигурации;

- Встроенная высокоскоростная статическая память с доступом за один тактовый цикл на максимальной тактовой частоте и объёмом от 64 до 32 Кб;

- Интерфейс внешней памяти (для устройств AT32UC3A0) SDRAM/SRAMсовместимая шина памяти (16-раз-

- рядные шины данных и 24-разрядная шина адресов);

- Контроллер прерываний с автоматически векторизуемыми прерываниями, малым временем ожидания и программируемым приоритетом;

- Системные функции со следующими особенностями:

- менеджер питания и синхронизации, включающий внутренний RC-генератор и генератор с частотой 32 кГц;

- два многоцелевых генератора и две системы ФАПЧ;

- независимые тактовые частоты для ЦПУ и USB;

- сторожевой таймер, таймер реального времени;

- Универсальная последовательная шина (USB) со следующими особенностями:

- полноскоростное USB-устройство версии 2.0 On-The-Go (OTG) с поддержкой полноскоростного и низкоскоростного режимов;

- гибкая конфигурация конечной точки USB и управление выделенными каналами DMA;

- приёмопередатчики на кристалле, включая подтянутые к «плюсу» питания резисторы;

- Интерфейс Ethernet MAC 10/100 Мбит/с со следующими особенностями:

- контроллер Ethernet MAC 802.3;

- поддержка МІІ и RMII;

- Один 16-разрядный таймер/счётчик (ТС) с тремя каналами со следующими особенностями:

- три внешних входа синхронизации, ШИМ, захват и различные возможности счёта событий;

- один 16-разрядный контроллер ШИМ с 7 каналами;

- Четыре универсальных синхронных/асинхронных приёмопередатчика (USART) со следующими особенностями:

- встроенный генератор скорости обмена, поддержка IrDA и интерфейса ISO7816;

- поддержка аппаратной процедуры установления связи, модемного интерфейса и интерфейса RS-485;

- Два ведущих/ведомых последовательных периферийных интерфейса (SPI) с сигналами выбора устройства;

- Один контроллер синхронного последовательного протокола с поддержкой I2S и универсального фреймового протокола;

- Один ведущий/ведомый двухпроводный интерфейс (TWI) с максимальной скоростью обмена 400 Кбит/с, совместимый с РС;

- Один 10-разрядный модуль 8-канального АЦП;

- Потоковый выход для 16-разрядного 2-канального звукового ЦАП с частотой выборки до 50 кГц;

- Встроенная система отладки (JTAGинтерфейс) на кристалле (OCD) с возможностью трассировки в реальном масштабе времени, доступа к памяти для чтения-записи на полной скорости в дополнение к основной отладке во время выполнения кода;

- Исполнение в 100-выводном корпусе TQFP (69 линий GPIO), 144-выводном корпусе LQFP (109 линий GPIO);

- Толерантные к внешнему напряжению 5 В линии ввода-вывода;

- Единственное напряжение питания 3,3 В или два напряжения питания 1,8 и 3,3 В;

Устройства подсемейства AT32UC3B имеют следующие типовые характеристики [4, 5]:

- Высокоэффективное 32-разрядное процессорное ядро с оригинальной архитектурой AVR32 и следующими особенностями:

- компактная система команд RISC, выполняющихся за один тактовый цикл, включая команды DSP;

- команды «чтение-модификациязапись» и команды манипуляций с битами;

- тактовая частота до 60 МГц при удельной производительности 1,38 DMIPS/МГц;

- производительность 75 DMIPS при выполнении программы из флэш-памяти с тактовой частотой 60 МГц;

- производительность 45 DMIPS при выполнении программы из флэш-памяти с тактовой частотой 33 МГц;

- модуль защиты памяти (MPU);

- Мультииерархическая шинная система со следующими особенностями:

- высокоэффективный обмен данными по отдельным шинам для повышения производительности;

- семь каналов DMA для автоматической передачи данных;

- Встроенная высокоскоростная флэш-память со следующими особенностями:

- объём от 256 до 64 Кб;

- доступ за один тактовый цикл на тактовой частоте до 30 МГц;

- буфер выборки с упреждением для оптимизации выполнения команд на максимальной тактовой частоте;

- время программирования страницы 4 мс, время стирания всего кристалла 8 мс;

- 100 000 циклов записи, 15-летний срок сохранности данных;

- ключи защиты памяти и задаваемые пользователем области конфигурации:

- Встроенная высокоскоростная статическая память с доступом за один тактовый цикл на максимальной тактовой частоте и объёмом от 32 до 16 Кб;

- Контроллер прерываний с автоматически векторизуемыми прерываниями, малым временем ожидания и программируемым приоритетом;

- Системные функции со следующими особенностями:

- менеджер питания и синхронизации, включающий внутренний RC-генератор и генератор с частотой 32 кГц;

- два многоцелевых генератора и две системы ФАПЧ;

- независимые тактовые частоты для ЦПУ и USB;

- сторожевой таймер, таймер реального времени;

- Универсальная последовательная шина (USB) со следующими особенностями:

- полноскоростное USB-устройство версии 2.0 On-The-Go (ОТG) с поддержкой полноскоростного и низкоскоростного режимов;

- гибкая конфигурация конечной точки USB и управление выделенными каналами DMA;

- приёмопередатчики на кристалле, включая подтянутые к «плюсовому» питанию резисторы;

- Один 16-разрядный таймер/счётчик (ТС) с тремя каналами со следующими особенностями:

- три внешних входа синхронизации, ШИМ, захват и различные возможности счёта событий;

- один 16-разрядный контроллер ШИМ с 7 каналами;

- Три универсальных синхронных/асинхронных приёмопередатчика (USART) со следующими особенностями:

- встроенный генератор скорости обмена, поддержка IrDA и интерфейса ISO7816;

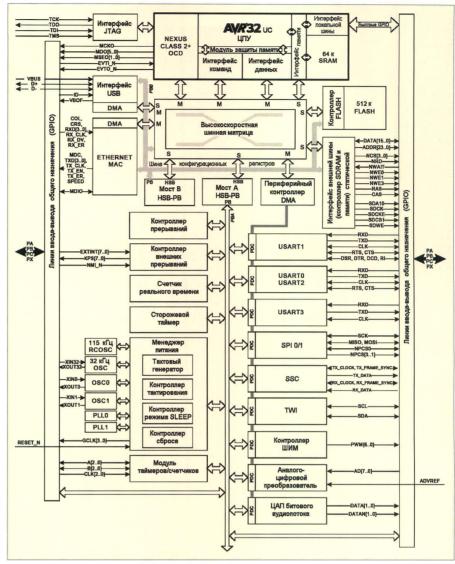

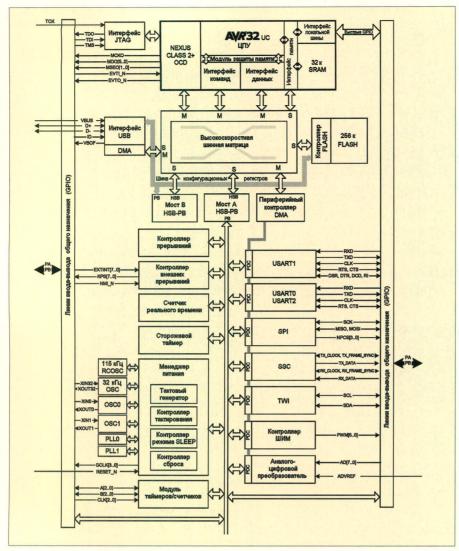

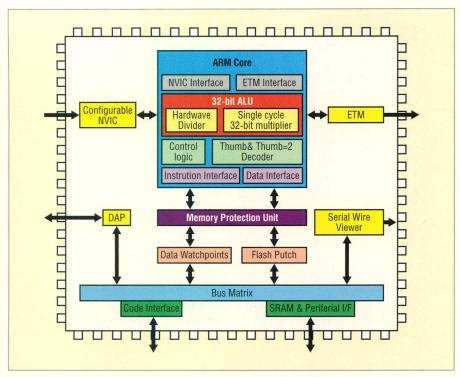

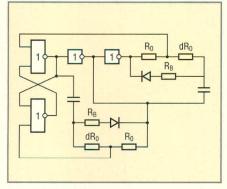

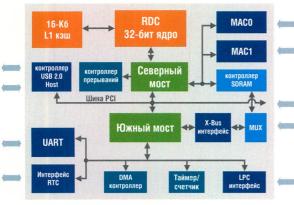

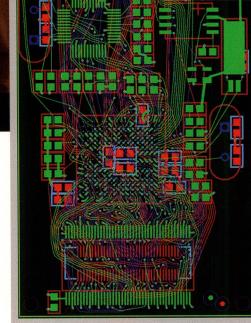

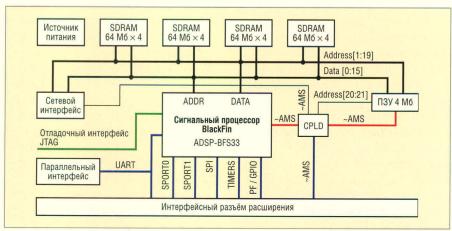

Рис. 1. Блок-схема МК подсемейства AT32UC3A

- поддержка аппаратной процедуры установления связи, модемного интерфейса и интерфейса RS-485;

- Один ведущий/ведомый последовательный периферийный интерфейс (SPI) с сигналами выбора устройства;

- Один контроллер синхронного последовательного протокола с поддержкой I2S и универсального фреймового протокола;

- Один ведущий/ведомый двухпроводный интерфейс (TWI) с максимальной скоростью обмена 400 кбит/с, совместимый с I<sup>2</sup>C;

- Один 10-разрядный модуль 8-канального АЦП;

- Встроенная система отладки (JTAGинтерфейс) на кристалле (OCD) с возможностью трассировки в реальном масштабе времени, доступа к памяти для чтения-записи на полной скорости в дополнение к основной отладке во время выполнения кода;

- Исполнение в 64-выводном корпусе TQFP/QFN (44 линии GPIO), 48-выводном корпусе TQFP/QFN (28 линий GPIO);

- Толерантные к внешнему напряжению 5 В линии ввода-вывода, включая четыре вывода с драйверами повышенной нагрузочной способности;

- Единственное напряжение питания 3,3 В или два напряжения питания 1,8 и 3,3 В.

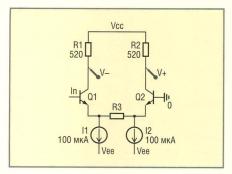

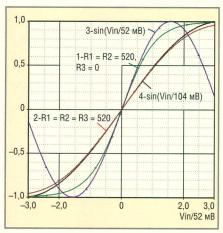

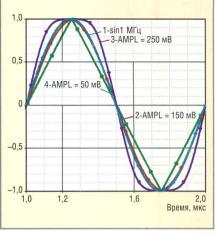

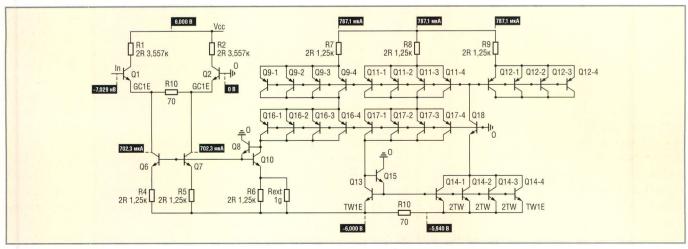

Блок-схема МК подсемейства AT32UC3A показана на рисунке 1, а МК подсемейства AT32UC3B – на рисунке 2.

### **А**РХИТЕКТУРА И ПРОГРАММНАЯ МОДЕЛЬ **AVR32**

AVR32 представляет собой высокоэффективную 32-разрядную RISC-архитектуру, предназначенную для встраиваемых приложений, с упором на потребление малой мощности и высокую плотность кода. По утверж-

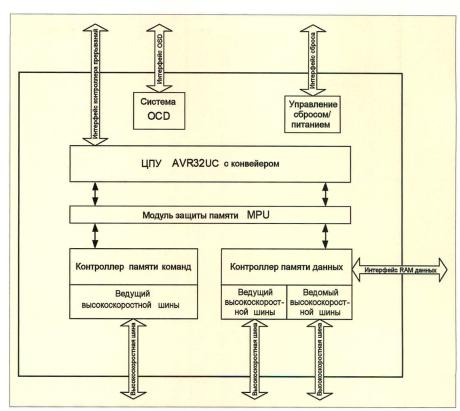

Рис. 2. Блок-схема МК подсемейства АТЗ2UС3В

дению производителя, архитектура AVR32 обеспечивает наилучшую плотность кода в своём классе устройств [6, 7].

Как уже было сказано, процессорное ядро AVR32UC заявлено первым промышленно выпускаемым ядром, которое объединяет чтение-запись SRAM за один тактовый цикл с прямым интерфейсом к ЦПУ. Этот интерфейс обходит системную шину, что позволяет достигнуть в AVR32 максимальной скорости выполнения программы, детерминизма цикла и минимальной потребляемой мощности. Наличие в ядре интерфейса ведомого к высокоскоростной шине (HSB) позволяет контроллерам DMA или другим ведущим устройствам HSB обмениваться данными непосредственно с встроенным в процессор статическим ОЗУ. Если ЦПУ и ведомое устройство HSB запрашивают доступ одновременно, предусмотрен арбитраж. Для нужд приложений в системе реализована программируемая схема приоритетов.

Процессор поддерживает операции с байтами и полусловами данных без необходимости выполнения дополнительного объёма программного кода. Запись в память и чтение памяти обеспечиваются для байта, полуслова, слова и двойного слова данных с автоматическим признаком или дополнением нулями свободных полей полуслова или байта. Архитектура AVR32 разрабатывалась с учётом специфики работы компилятора Си, что даёт возможность в полной мере использовать его возможности по оптимизации кода.

Чтобы уменьшить размер кода до минимума, некоторые команды AVR32 имеют множественные способы адресации. Например, команды с непосредственной адресацией часто имеют компактный формат с меньшим непосредственным значением и расширенный формат с большим непосредственным значением. Используя эту особенность, компилятор подбирает формат, дающий наименьший размер кода.

Другая особенность системы команд состоит в том, что часто используемые команды, например, команды сложения, загрузки и сохранения имеют компактный формат с двумя операндами и расширенный формат с тремя операндами. Расширенный формат увеличивает производительность, позволяя осуществлять добавление и перемещение данных единственной командой за один цикл.

Регистровый файл процессора организован как шестнадцать 32-разрядных регистров и включает в себя программный счётчик, регистр связи и регистр-указатель вершины стека. Кроме того, регистр R12 предназначен для хранения возвращаемых значений при вызове функций и неявно используется некоторыми командами.

В микроконтроллерах семейства AT32UC3 процессорное ядро с архитектурой AVR32UC интегрирует расширенную систему отладки (ОСD), содержит модуль защиты памяти (MPU), но в отличие от архитектуры семейства AVR32A не содержит встроенной кэш-памяти. Аппаратный ускоритель команд языка Java в МК семейства AT32UC3 также не реализован.

Микроконтроллеры семейства AT32UC3 поддерживают три интерфейса памяти: один ведущий интерфейс к высокоскоростной шине (HSB) для выборки команд, один ведущий интерфейс к высокоскоростной шине для доступа к данным и один ведомый интерфейс к высокоскоростной шине для доступа к статической памяти, встроенной в центральный процессор. Хранение данных в этой памяти позволяет осуществить быстрый доступ к ним, уменьшает время ожидания и гарантирует правильную синхронизацию. Кроме того, указанная особенность архитектуры уменьшает потребляемую мощность, поскольку для доступа к SRAM не требуется полностью задействовать высокоскоростную системную шину. Специализированный интерфейс внешнего ОЗУ данных реализован в архитектуре для того, чтобы осуществлять обмен данными со встроенной SRAM.

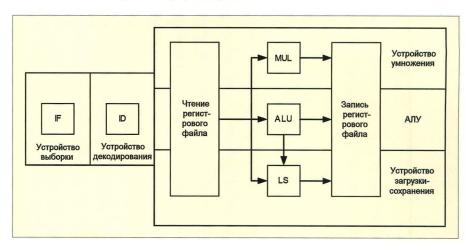

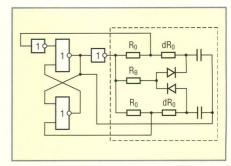

Блок-схема центрального процессора устройств семейства AT32UC3 показана на рисунке 3. Процессор МК типа AT32UC3 имеет трёхступенчатый конвейер обработки команд. Конвейер состоит из следующих стадий: выборка команды (IF), декоди-

рование команды (ID) и выполнение команды (EX). Большинство команд выбирается, декодируется и выполняется за один тактовый цикл. Выполнение некоторых команд требует нескольких тактовых циклов, и в этом случае команда постоянно находится в стадиях ID и EX конвейера в течение требуемого числа тактовых циклов.

Стадия выборки команды была специально разработана, чтобы оптимизировать вызов команды из флэш-памяти. При выборке в каждом тактовом цикле происходит запись одной 32-разрядной или двух 16-разрядных команд во внутренний буфер команд. Наличие этого буфера гарантирует отсутствие остановов конвейерной обработки в ходе последовательного выполнения программы.

На следующей стадии происходит декодирование команды и генерация необходимых сигналов для её выполнения.

Третья стадия разбита на три параллельных секции (модуля): арифметическую секцию - арифметикологическое устройство (ALU), секцию умножения (MUL) и секцию загрузки/сохранения (LS). Арифметикологическое устройство выполняет арифметические и логические операции, включая аппаратное деление. Модуль умножения выполняет операции умножения и умножения с накоплением (МАС), поддерживаемые системой команд. Модуль загрузки/сохранения выполняет операции доступа к SRAM или операции доступа к высокоскоростной шине (HSB) за один тактовый цикл. Регистры регистрового файла могут быть модифицированы в течение того же самого тактового цикла, в котором происходит выполнение команды. Эта особенность упрощает программную трансляцию по сравнению с более длинными конвейерами, поскольку отсутствует необходимость в планировании кода.

Блок-схема обработки команд в конвейере показана на рисунке 4. Архитектуры AVR32UC и AVR32A используют одну и ту же 16/32-разрядную систему команд (ISA) с более чем 220 командами, доступными как 16-разрядные компактные и 32-разрядные расширенные команды. Система команд этого ядра обеспечивает управление единичными разрядами для контроля встроенной перифе-

Рис. 3. Блок-схема центрального процессора устройств семейства AT32UC3

Рис. 4. Блок-схема обработки команд в конвейере

рии, интерфейсов ввода/вывода общего назначения и целочисленных арифметических модулей DSP, в том числе однотактных умножителей с накоплением.

Команды DSP ISA в архитектуре AVR32UC выполняются в модуле умножения за один тактовый цикл. Сюда входят команды умножения и команды умножения с накоплением для стандартных и дробных чисел, с/без переполнения и округления. Результат умножения или умножения с накоплением может иметь размер 32, 48 или 64 разряда, при этом 48- и 64-разрядный результат помещается в два регистра. К командам DSP также относятся команды сложения и вычитания, а также команды форматирова-

ния данных типа сдвига данных с переполнением и округлением.

Процессор архитектуры AVR32UC может работать в привилегированном или непривилегированном режимах. Привилегированный режим часто используется для ОС реального времени, позволяя осуществлять доступ ко всем системным ресурсам и использовать отдельный системный стек. Непривилегированный режим применяется для выполнения приложений и ограничивает доступ к некоторым из системных ресурсов.

Блок-схема регистрового файла архитектуры AVR32UC показана на рисунке 5. В верхней строке над каждым столбцом указано название режима процессора, в котором доступен на-

| Прикладной пользовательский | Супервизор<br>(Supervisor) | INT0         | INT1         | INT2         | INT3         | Исключение<br>(Exception) | NMI          |

|-----------------------------|----------------------------|--------------|--------------|--------------|--------------|---------------------------|--------------|

| (Application) Bit 31 Bit 0  | Bit 31 Bit 0               | Bit 31 Bit 0 | Bit 31 Bit 0 | Bit 31 Bit 0 | Bit 31 Bit 0 | Bit 31 Bit 0              | Bit 31 Bit 0 |

| PC                          | PC                         | PC           | PC           | PC           | PC           | PC                        | PC           |

| LR                          | LR                         | LR           | LR           | LR           | LR           | LR                        | LR           |

| SP_APP                      | SP_SYS                     | SP_SYS       | SP_SYS       | SP_SYS       | SP_SYS       | SP_SYS                    | SP_SYS       |

| R12                         | R12                        | R12          | R12          | R12          | R12          | R12                       | R12          |

| R11                         | R11                        | R11          | R11          | R11          | R11          | R11                       | R11          |

| R10                         | R10                        | R10          | R10          | R10          | R10          | R10                       | R10          |

| R9                          | R9                         | R9           | R9           | R9           | R9           | R9                        | R9           |

| R8                          | R8                         | R8           | R8           | R8           | R8           | R8                        | R8           |

| R7                          | R7                         | R7           | R7           | R7 R7        |              | R7                        | R7           |

| R6                          | R6                         | R6           | R6           | R6           | R6           | R6                        | R6           |

| R5                          | R5                         | R5           | R5           | R5           | R5           | R5                        | R5           |

| R4                          | R4                         | R4           | R4           | R4 R4        |              | R4                        | R4           |

| R3                          | R3                         | R3           | R3           | R3           | R3           | R3                        | R3           |

| R2                          | R2                         | R2           | R2           | R2           | R2           | R2                        | R2           |

| R1                          | R1                         | R1           | R1           | R1           | R1           | R1                        | R1           |

| R0                          | R0                         | R0           | R0           | R0           | R0           | R0                        | R0           |

| SR                          | SR                         | SR           | SR           | SR           | SR           | SR                        | SR           |

Рис. 5. Блок-схема регистрового файла архитектуры AVR32UC

бор регистров, перечисленных в соответствующем столбце; 32-разрядный регистр состояния (SR) разбит на два полуслова (старшее и младшее). Младшее полуслово состояния содержит флаги-признаки операций, а также код состояния, образуемый несколькими флагами состояния. Старшее полуслово содержит информацию о режиме процессора и состоянии выполнения программы в нём.

Процессор AVR32UC содержит мощную схему обработки исключений. Различные источники исключений, например, некорректный код операции или внешние запросы прерываний, имеют различные уровни приоритета, тем самым гарантируя предсказуемое поведение системы, когда одновременно генерируется множество исключений. Кроме того, ждущие обработки

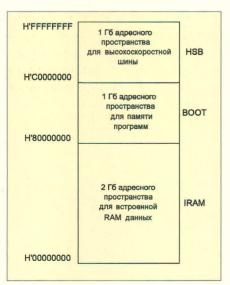

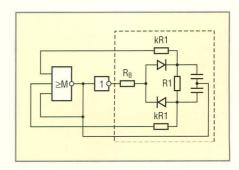

Рис. 6. Карта 32-разрядного адресного пространства памяти AVR32UC

исключения с более высоким приоритетом могут прервать текущую обработку исключений с более низким приоритетом. Когда это происходит, выполнение потока команд программы приостанавливается, а управление выполнением передаётся обработчику события с собственным адресом.

Все внешние источники прерывания имеют автоматически векторизуемый адрес программы обработки прерывания (ISR).

При обработке событий в процессоре AVR32UC, как и во всех прочих устройствах архитектуры AVR32A, использует системный стек. На вершину этого стека указывает регистр – указатель вершины стека SP\_SYS. Стек используется для сохранения и выгрузки регистров R8-R12, LR, регистра состояния и адреса возврата.

#### ОРГАНИЗАЦИЯ ПАМЯТИ

Устройства архитектуры AVR32UC имеют встроенную высокоскоростную флэш-память объёмом от 512 Кб (AT32UC3A0512, AT32UC3A1512) до 64 Кб (AT32UC3B064, AT32UC3B164).

Помимо флэш-памяти, устройства AVR32UC также имеют встроенную высокоскоростную статическую память с доступом за один тактовый цикл при максимальной тактовой частоте и с объёмом от 64 Кб (AT32UC3A0512, AT32UC3A1512, AT32UC3A0256, AT32UC3A1256) до 16 Кб (AT32UC3B064, AT32UC3B164).

Системная шина устройств AVR32UC физически реализована как шинная матрица. Все системные адреса шины являются фиксированными и не могут

быть переотображены никогда, даже при начальной загрузке.

Карта 32-разрядного адресного пространства памяти AVR32UC показана на рисунке 6. Как можно видеть, пространство памяти содержит три раздела: IRAM, BOOT и HSB. Раздел IRAM содержит внутреннюю память стадии ЕХ-конвейера, которая отображена с адреса 0 в сторону возрастания адресов. Раздел ВООТ начинается с адреса 0х8000\_0000, который является адресом сброса для процессора AVR32UC. Этот раздел содержит встроенную флэш-память программ, отображённую с адреса 0х8000 0000 в сторону возрастания адресов. Раздел HSB содержит адреса специальных регистров пользовательских интерфейсов всех модулей МК, отображённых на шину HSB. Сюда относятся периферийные устройства типа USART и внешних интерфейсов памяти.

Пространство памяти однородно, поэтому код программы может выполниться в любом из этих трёх разделов. Доступ к данным также может быть выполнен в любом из них. Однако в МК типа AVR32UC можно запретить определённые виды доступа к некоторым разделам памяти, например, запись во флэш-память раздела ВООТ.

Центральный процессор архитектуры AVR32UC включает в себя три интерфейса памяти:

- стадия ІF конвейера имеет интерфейс ведущего к шине HSB для выборки команд;

- стадия EX конвейера имеет интерфейс ведущего к шине HSB для до-

ступа к данным из раздела памяти BOOT или из раздела памяти HSB;

стадия ЕХ конвейера имеет интерфейс ведомого к шине HSB, позволяющий осуществлять доступ других модулей системы к адресам из раздела памяти IRAM.

#### **О**РГАНИЗАЦИЯ ЭЛЕКТРОПИТАНИЯ

Для питания МК семейства AT32UC3 в общем случае требуется два напряжения:

- 3,6 В для питания устройств вводавывода и аналоговой части;

- 1,8 В для питания процессорного ядра, памяти, ФАПЧ и периферии.

Использование входящего в состав AT32UC3 встроенного стабилизатора с выходным напряжением 1,8 В позволяет отказаться от одного из внешних источников.

Для всех МК фирмы Atmel характерно наличие расширенных возможностей управления энергопотреблением, реализованных, как правило, посредством управления тактированием устройства. Семейство AT32UC3 не является исключением. Управление энергопотреблением в AT32UC3 обеспечивается встроенным модулем менеджера питания (РМ), который вклю-

чает в себя два высокочастотных кварцевых генератора, две системы ФАПЧ, ультранизкопотребляющий генератор частоты 32 кПц, а также RC-генератор. Менеджер питания поддерживает избирательное тактирование на уровне модулей МК, обеспечивает возможность «пробуждения» ЦПУ от внутренних или внешних прерываний, а также поддерживает несколько вспомогательных режимов «спящего» режима (Sleep), позволяющих производить избирательное отключение логики синхронизации, систем ФАПЧ и генераторов в различных сочетаниях.

Все генерируемые в модуле РМ импульсные сигналы делятся на сигналы синхронизации и универсальные сигналы. Сигналы синхронизации используются для синхронизации основной цифровой логики МК (ЦПУ и периферийные модули, связанные с шинами НЅВ, РВА и РВВ). Универсальные сигналы являются асинхронными и могут быть заданы в пределах широкого диапазона частот, что делает их подходящими для тактирования периферийных устройств, например, коммуникационных модулей и таймеров.

Встроенный в МК семейства AT32UC3 модуль сторожевого таймера (WDT)

синхронизируется от встроенного RC-генератора.

Продолжение следует

#### ЛИТЕРАТУРА

- 1. *Курилин A*. AVR32: новый микроконтроллер для мультимедийных приложений. Электронные компоненты. 2006. № 9 (http://www.atmel.ru/Articles/Atmel35.htm).

- 2. *Королев Н., Шабынин А.* Архитектура AVR: развитие вширь и вглубь. Часть 2. Компоненты и технологии. 2007. № 4 (http://www.argussoft.ru).

- 3. AVR\*32 32-Bit Microcontroller AT32UC3A0512, AT32UC3A0256, AT32UC3A0128, AT32UC3A1512, AT32UC3A1256, AT32UC3A1128 Preliminary. 32058C-AVR32-10/07, http://www.atmel.com.

- 4. AVR\*32 32-Bit Microcontroller AT32UC3B0256, AT32UC3B0128, AT32UC3B064, AT32UC3B1256, AT32UC3B1128, AT32UC3B164 Preliminary. 32059E-AVR32-12/07, http://www.atmel.com.

- 5. http://www.avr32.ru.

- AVR32 Architecture Document 32000B-AVR32-11/07, http://www.atmel.com.

- 7. AVR32UC Technical Reference Manual. 3 2 0 0 2 C A V R 3 2 1 1 / 0 7 , http://www.atmel.com.

#### Hoвости мира News of the World Новости мира

# Понижающий 40-В преобразователь для мощных светодиодов

Фирма Prema Semiconductor представляет индуктивную схему управления светодиодами PR4101. Преобразователь управляет одним или несколькими светодиодами токами от 100 мА до нескольких ампер в зависимости от выбора внешней схемы. Напряжение источника напряжения 9...40 В. Схема управления пригодна как для приложений с батареями 12 или 24 В, так и для осветителей, которые раньше комплектовались галогенными лампами с трансформаторами. Нормальный диапазон рабочих напряжений PR4101 со-

ставляет 9...40 В постоянного напряжения. Но при использовании дополнительных внешних элементов возможна также работа непосредственно от источника переменного напряжения 12 или 24 В (50 или 60 Гц). РR4101 пригоден как для самых различных осветителей на светодиодах, так и для задней подсветки ЖК-дисплеев. В зависимости от приложения он может применяться в двух исполнениях: или со всеми функциями в корпусе SO14, или в сокращённом варианте (без входа Power-Down и PWM) в корпусе SO8.

www.prema.com

# Светодиоды янтарного и жёлтого цвета с яркостью 2,859 кд

Фирма Vishay предлагает серию светодиодов поверхностного монтажа. Элементы серии VLMx32 выпускаются в корпусе PLCC4 с оптимизированной рамкой, имеющем тепловое сопротивление до 290 К/Вт и мощность рассеяния до 200 мВт, что обеспечивает возможность эксплуатации этих светодиодов с токами до 70 мА. Светодиоды по своим параметрам соответствуют

АЕС-Q101 и поэтому пригодны для автомобильных приложений. Янтарные и жёлтые светодиоды предназначены для таких приложений, как внутреннее и внешнее освещение светофоров и дорожных знаков, системы освещения автомобилей; индикаторы и задняя подсветка для аудио-, видеои телекоммуникационных устройств и офисного оборудования, ЖК-дисплеи, подсветка переключателей и индикация символов. Устройства на светодиодах обеспечивают силу света от 1,400 до 2,850 кд при длине волны 610...621 нм (янтарные) или 585...594 нм (жёлтые).

www.vishay.com

# Введение в архитектуру Cortex-M3

(часть 1)

Печатается с разрешения журнала Chip News Украина (www.chipnews.com.ua)

#### Павел Вовк (Киев, Украина)

Однокристальные решения, выполненные на основе встроенных ARM-процессоров, находят своё применение в самых различных областях рынка, включая такие ресурсоёмкие сегменты, как корпоративные приложения, автомобильные системы, домашние и беспроводные сетевые технологии и многие другие. Семейства процессоров на базе архитектуры ARM Cortex обеспечивают необходимые ресурсы для решения такого широкого круга задач.

Семейство процессоров Cortex включает в себя три основных подсемейства архитектуры ARMv7: подсемейство А для очень ресурсоёмких приложений, выполняемых под управлением сложных операционных систем, подсемейство R для применения в системах реального времени и подсемейство М, оптимизированное для применения в недорогих встроенных приложениях.

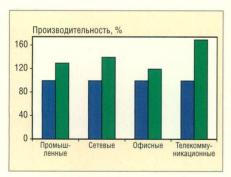

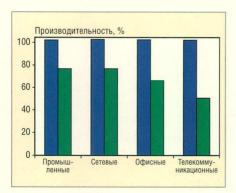

Рис. 1. Сравнение производительности стандартных ARM-процессоров ARM7TDMI-S (ARM) и процессоров Cortex-M3 (Thumb-2) в типовых приложениях

Рис. 2. Сравнение объёма кода стандартных ARM-процессоров ARM7TDMI-S (ARM) и процессоров Cortex-M3 (Thumb-2) для типовых приложений

Процессоры семейства Cortex-M3 первые ARM-процессоры, базирующиеся на архитектуре ARMv7-M, которые были специально спроектированы для достижения высокой произволительности всей системы в недорогих высокоэкономичных встроенных приложениях, таких как, например, системы промышленного контроля, автомобильная электроника, проводные и беспроводные телекоммуникационные системы, системы управления электроприводами и т.п. Для достижения этой цели было внесено множество изменений в базовую архитектуру, в частности, существенно упрощён процесс создания программного кода, что сделало рентабельным применение процессоров на базе архитектуры Cortex-M3 даже в самых простых приложениях.

Для увеличения производительности системы процессоры должны либо работать с более высокой тактовой частотой, либо использовать более изощрённые методы увеличения эффективности вычислений. Повышение тактовой частоты в принципе может повысить производительность, но в то же время увеличивает энергопотребление и сложность применения. С другой стороны, повышение эффективности вычислений при более низкой тактовой частоте более предпочтительно.

В основе процессора на базе архитектуры Cortex-M3 лежит ядро, выполненное по гарвардской технологии с трёхступенчатым конвейером. Это обеспечивает такие

привлекательные возможности, как предсказание переходов, однотактное умножение и аппаратно реализованное деление, увеличивающие производительность до 1,25 MIPS/МГц (в тесте Drystone). В процессорах Cortex-M3 реализован новый набор команд Thumb-2, что позволяет достигнуть на 70% большей производительности на мегагерц, чем у классических ARM-процессоров на базе ARM7TDMI-S, использующих классический набор команд Thumb, и на 35% большей производительности, чем у тех же процессоров, выполняющих базовый набор команд ARM (по данным того же теста Drystone).

Сокращение времени выхода конечного продукта на рынок и снижение затрат на разработку являются важнейшими критериями при выборе процессора; точно так же возможность быстро и легко создавать программный код является одним из ключевых требований в этом вопросе.

Процессоры на базе архитектуры Cortex-M3 разрабатывались с целью обеспечить как можно более быстрое и простое создание эффективного программного кода без использования ассемблерных вставок, при этом от программиста не требовалось очень глубокого знания особенностей архитектуры процессора для создания приложений средней сложности. Данные процессоры используют упрощённую стековую модель программирования, в которой удалось совместить стандартные команды ARM с несколько переработанными и адаптированными к ядру ARM идеями, применявшимися в 8- и 16-разрядных микроконтроллерах, доказавшими свою высокую эффективность. В то же время аппаратно реализованное управление прерываниями позволяет создавать очень простые обработчики прерываний без использования ассемблерных вставок или каких-либо манипуляций с регистрами.

Новой, ключевой особенностью системы команд Thumb-2 является более эффективная реализация компилятора языка С с возможностью операций с битами и битовыми полями, аппаратным делением и более эффективной реализацией конструкций условий типа if/then. С точки зрения разработчика программного кода, процессоры с набором команд Thumb-2 позволяют создавать код намного быстрее, проще и эффективнее. Более того, при использовании набора команд Thumb-2 и соответствующего компилятора больше не придётся делать мучительный выбор между оптимизацией кода по скорости или по объёму - в новых компиляторах возможна оптимизация как по объёму, так и по скорости. Это еще более ускоряет процесс разработки программного кода, так как теперь программистам нет нужды заранее компилировать критические участки кода и присоединять их к основной программе в виде библиотек.

Постоянным ограничением в применении более производительных процессоров является их стоимость. Сравнение ядер ARM7TDMI-S и Cortex-M3

| T. Bourse                          | Ядро                |                                         |  |  |  |  |

|------------------------------------|---------------------|-----------------------------------------|--|--|--|--|

| Параметр                           | ARM7TDMI-S          | Cortex-M3                               |  |  |  |  |

| Ядро                               | ARMv4T              | ARMv7-M                                 |  |  |  |  |

| Архитектура                        | фон Неймана         | Гарвардская                             |  |  |  |  |

| Поддерживаемые системы команд      | Thumb               | Thumb/Thumb-2                           |  |  |  |  |

| Прерывания                         | FIQ/IRQ             | NMI + от 1 до 240 физических прерываний |  |  |  |  |

| Время обработки прерывания, тактов | 2442                | 12                                      |  |  |  |  |

| Пошаговый режим                    | Нет                 | Интегрирован                            |  |  |  |  |

| Защита памяти                      | Нет                 | 8 региональных устройств защиты памяти  |  |  |  |  |

| Производительность, DMIPS/MГц      | 0,95 (в режиме ARM) | 1,25                                    |  |  |  |  |

| Потребляемая мощность, мВт/МГц     | 0,28                | 0,19                                    |  |  |  |  |

| Площадь кристалла, мм <sup>2</sup> | 0,62 (только ядро)  | 0,86 (ядро и стандартная периферия)     |  |  |  |  |

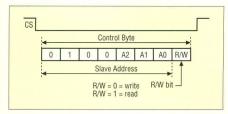

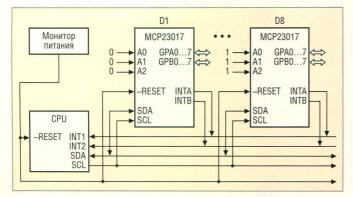

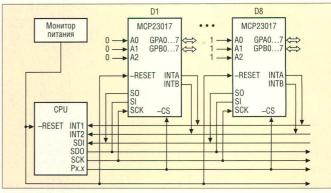

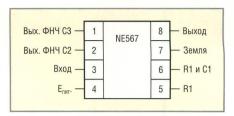

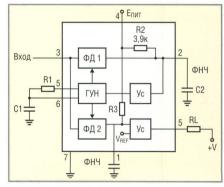

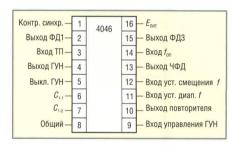

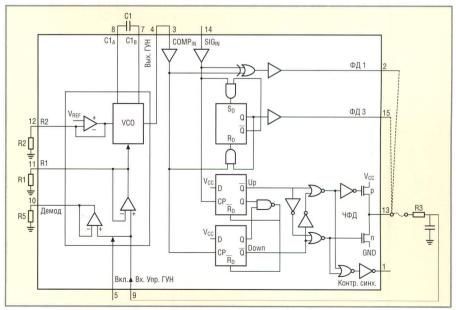

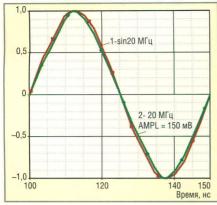

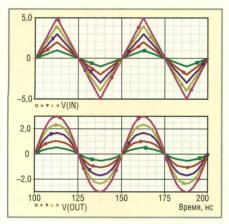

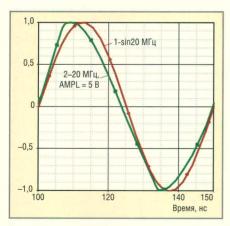

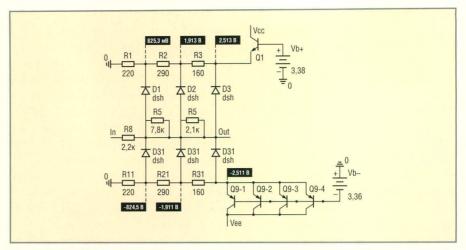

Современные технологии производства являются дорогостоящими, и поэтому решающим моментом в уменьшении стоимости процессора является площадь его кристалла. Процессоры, выполненные по технологии Согtex-М3, используют самое маленькое ядро ARM на сегодняшний день, содержащее всего 33 тыс. вентилей, выполненных по 0,18-мкм технологии, и уменьшенные до разумных размеров периферийные модули. Требования ядра к